お節介なパワーアンプの妖精が耳元で囁いた、雨上がりの虹の彼方にSITを待っているアンプがあると。

2SK182の二の舞は怖いから、一応の保護回路を備えたりして、ぼつぼつ再チャレンジの旅の計画の予定を立てる準備でも始めよっかな。

昨今の自作アンプは薄いあんちょこ頼りのファストフード的お手軽物ばかり、こんな体たらくな時代の風潮にビシッと一石を投じてやりたい。

主要な基本回路

バランス出力クロスシャント・プッシュプル

|

左図のバイアス回路を省略した模式図で動作を説明する。 記入した電圧振幅は理想動作でのフル出力の状態を表す。 TR1とTR2で構成する差動回路によって、コレクタにVG1とVG2が等振幅かつ逆位相で対称に発生する。 ここでは簡単に考えるため、SIT1とSIT2の ゲート・ソース間電圧を無視して、ゲートとソースを同電位と見なす。 SIT1のゲート電圧VG1はSIT1のソースに伝達され、それがSIT1のドレイン電源の電圧VD1で嵩上げされて出力電圧-Voとなる。

SIT2が導通してドレイン・ソース間電圧が0Vとなり、SIT1がカットオフしてドレイン・ソース間電圧がVD1+VD2となる最大出力の時、スピーカに掛かる電圧VSPはVD2である。 ここからが注目点! |

バイアス電圧制御ループ

|

左図の模式図でSITにバイアス電圧を与える基幹部分を説明する。 バランス動作するプッシュプル信号の中点には信号成分が含まれないことを利用して、RGI,RG2とRS1,RS2でSITのゲート電圧VG0とソース電圧VS0を検出する。 A1,A2は高インピーダンスで受けて低インピーダンスで 出力するゲイン1のバッファアンプであり、SITのゲート入力容量を強力にドライブするために設けてあり、RGI,RG2を接続しても負担にならない。 演算増幅器A3は、VS0よりも基準電圧VREF分だけ低い電圧とVG0が一致するように定電流源CC1,CC2を制御 して、SITのゲート・ソース間にVREFと等しいバイアス電圧を与える。

|

|

3極真空管特性のSITはドレイン・ソース間の電圧変化でドレイン電流が変化するため、ドレイン・ソース間電圧の変化に合わせてゲート・ソース間のバイアス電圧を変化させ、ドレイン電流を一定に保つ回路を取り入れた。

左図回路のSIT0のドレイン電流は、ソース側の定電流源IREFで固定しているために変化しない。 この回路のVREFを上の図のVREFに使うと、SIT1,SIT2とSIT0の特性が同じであれば、SIT1,SIT2のドレイン電流をIREFに等しくできる。 |

カレントミラー・プッシュプル・バランス出力型差動増幅回路

|

差動増幅回路をカレントミラー・プッシュプルのバランス出力とするために、差動回路のTR1とTR2のコレクタ電流をカスコード接続のTR3〜TR6で2つに

分岐し、2組のカレントミラー・プッシュプル回路のTR7〜TR10に与える。

|

アンプ回路の概略図

|

|

フロントエンド部分はバランス入力とアンバランス入力に対応、不要な高周波の入力を防ぐためfc=0.5MHzのハイカットフィルタを通し、ドライバ段に一定のNFBを掛ける必要からドライバ段の信号源インピーダンスを一定にするために、JFET入力OPアンプによるインスツルメンテーションアンプで入力信号電圧を受け取る。

ドライバ段がCMRの高い差動回路であるため、入力信号がアンバランスでもドライバ段でバランス信号に変換される。

ドライバ段のカレントミラー回路にブートストラップを掛けVCEを一定にして、高域特性や歪率の改善を図った。

SITのゲート電荷をドライブするためのバッファアンプはコンプリメンタリ・エミッタフォロワになっていて、その電源はSITのソース電位でブートストラップしている。

ファイナル段のSITのドレインにあるCB1,CB2は過大電流時に 回路を遮断してSITを保護する過電流保護回路で ある。

OUT-PUT直前のMSWは、出力の直流からスピーカを保護するために出力を遮断するミューティングスイッチで、オン抵抗が十数ミリΩと小さいMOS-FETスイッチを使用している。

バイアスコントロールはドライバ段の差動回路のカスコードトランジスタのエミッタに入力される電流を制御する。

このためドライバ段の差動回路の電流が、バイアスコントロール回路に分流する電流分だけ増すが、電流が増した分だけ差動回路のトランジスタのgmが増して直線性の改善に寄与する。

MOS-FETスイッチのシーケンス

MOS-FETスイッチは回路に組み込まれた動作条件とタイミングによってON/OFFする。

CB1,CB2をリセットするには、電源を落としてCB1,CB2に掛かる電圧を1V以下に低下させる必要があるが、CB1,CB2のトリップでSITのドレイン回路を遮断する

と、AC電源を切っても出力段電源の大容量ブロックコンデンサにチャージされた電圧が下がるまでは、CB1,CB2をリセットでき

ない状態が続く。

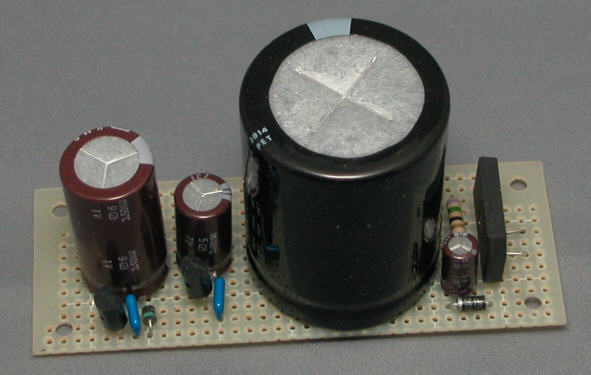

これでは使い勝手が悪いために、電源を切ると同時に出力段電源の大容量ブロックコンデンサ

を放電する回路を追加した。

回路

入力をバランス入力のXLRメスコネクタのみにして、アンバランス入力のRCAプラグには変換プラグで対応することにしました。

出力の一方がGNDに落ちると、中点電位がズレて適正なバイアスに制御できなくなるため、対策としてバランス出力両端子の中点から中点電位を検出するようにしました。

|

|

|

|

|

|

電源シーケンスの動作

電源スイッチをオンする、或いは電源スイッチをオンした状態で電源コードをACコンセントに接続するとかして電源が入ると、まだ出力段の電源トランスには通電されず、電圧増幅段などの電源トランスにだけ通電されます。

それによって、SITのバイアス電圧制御回路が動作してSITの電源電圧に合わせた適正なバイアス電圧に制御されます。

また同時に出力段電源回路のフォトカプラLEDに通電し、先ずブロックコンデンサの放電回路が切れます。

次に少しのタイミングを置いてラッシュカレント防止抵抗を通して出力段電源トランス1次側に通電し、更に少しのタイミングを置いてDCサプレッサのダイオードを通して出力段電源トランス1次側に通常のAC電圧がかかります。

出力段の電源電圧が上昇すると出力ミューティングMOS-FETスイッチのフォトカプラLEDに通電し、少しのタイミングを置いてアンプ出力が出力端子に発生します。

出力にDC電圧が発生した場合は、出力DC電圧検出回路がターンオンして、フォトカプラ経由で出力ミューティングのMOS-FETスイッチが切れます。

リセットするには一旦電源を切って入れ直します。

SITの過大ドレイン電流で過電流保護回路がトリップすると、SITのドレイン回路を遮断します。

過電流保護回路をリセットするには一旦電源を切って入れ直します。

電源が切れると小さい容量のコンデンサの放電時間で電圧低下を素早く検出して、出力段電源と出力ミューティングのMOS-FETスイッチが切れ、ブロックコンデンサの放電回路がオンします。

頻繁に幾度も電源の入切を繰り返すと、ブロックコンデンサの放電回路やラッシュカレント防止回路の抵抗やMOS-FETスイッチが発熱するので、放熱対策をしてあります。

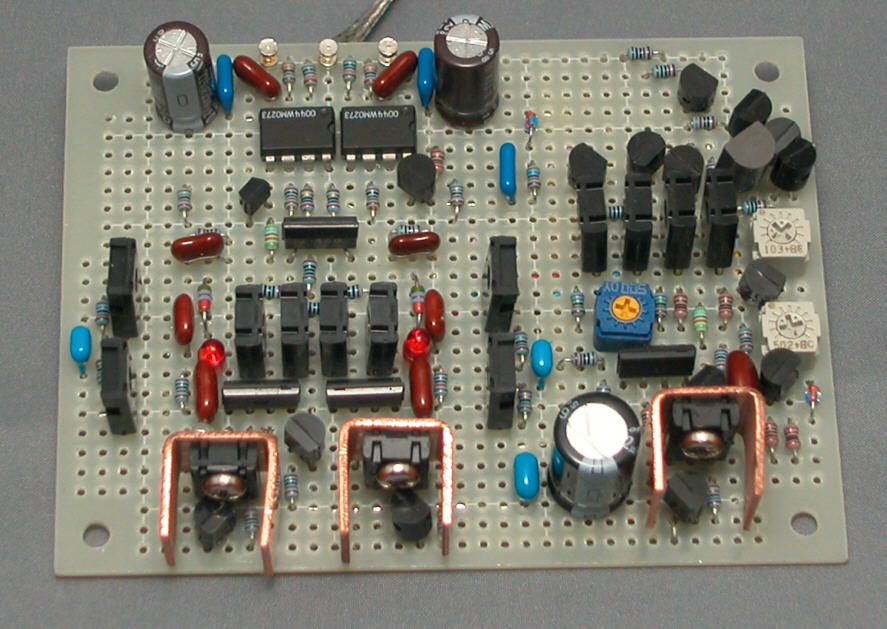

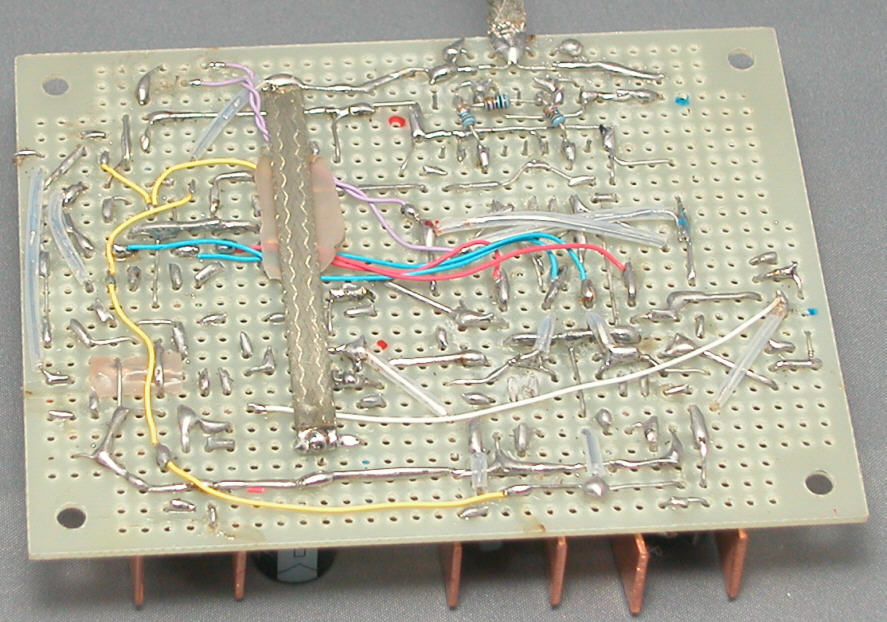

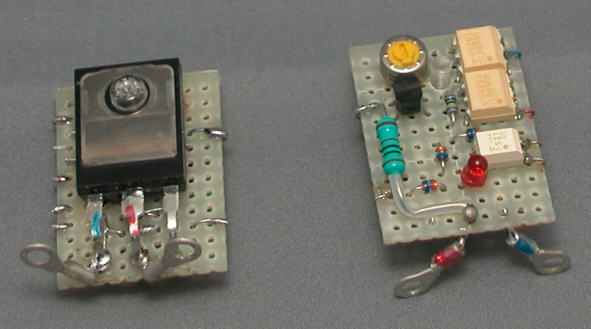

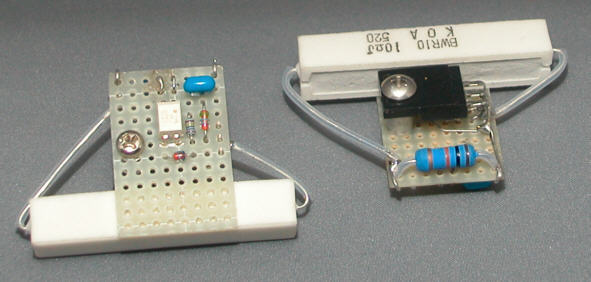

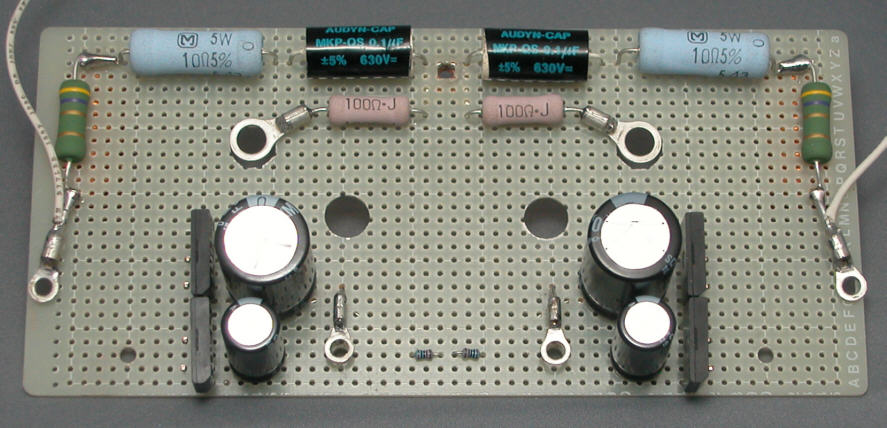

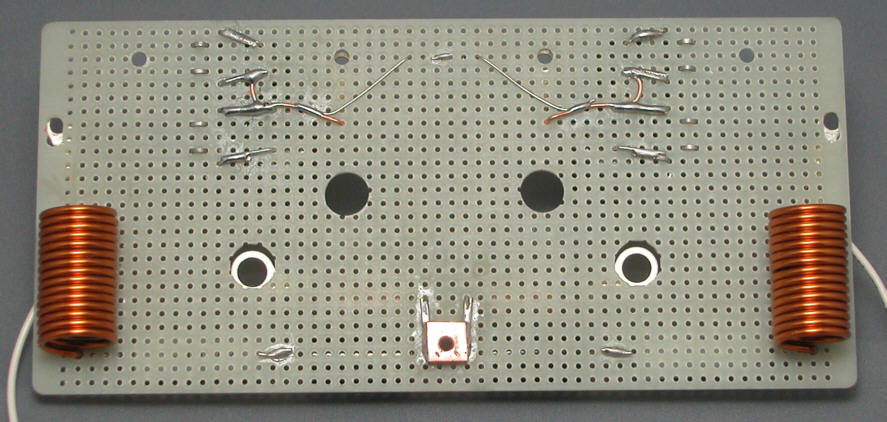

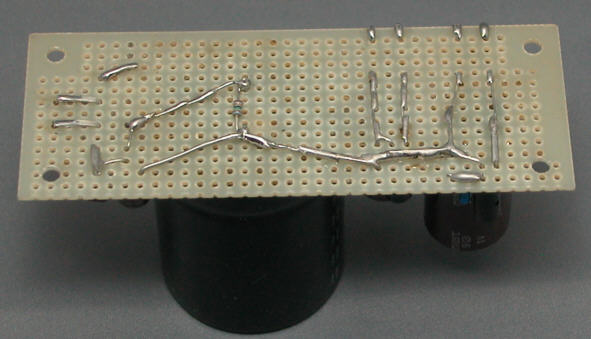

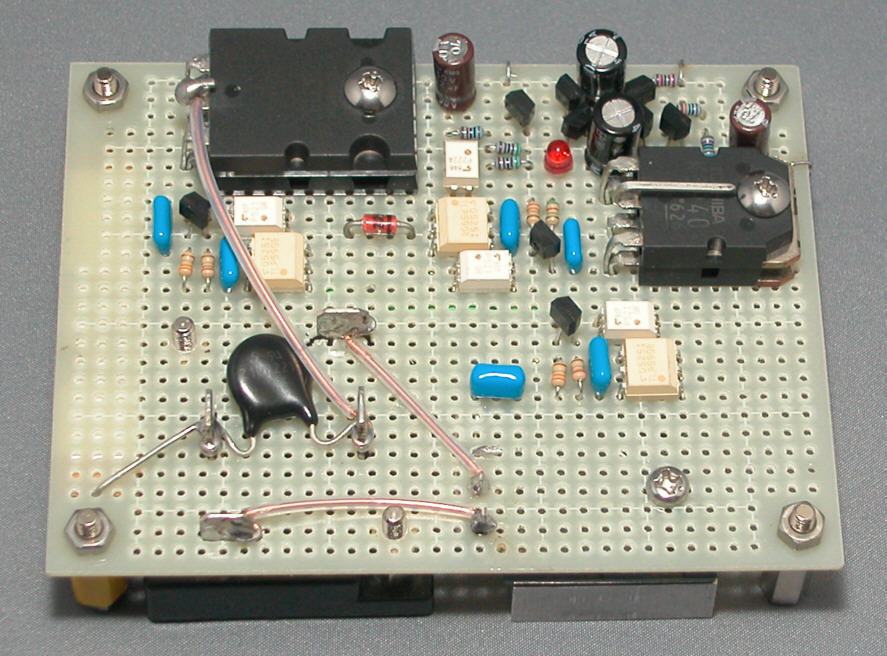

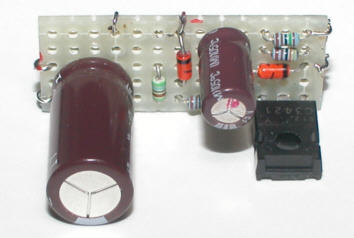

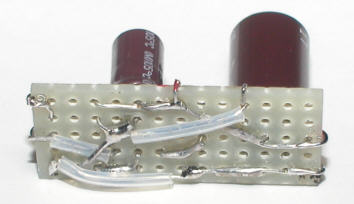

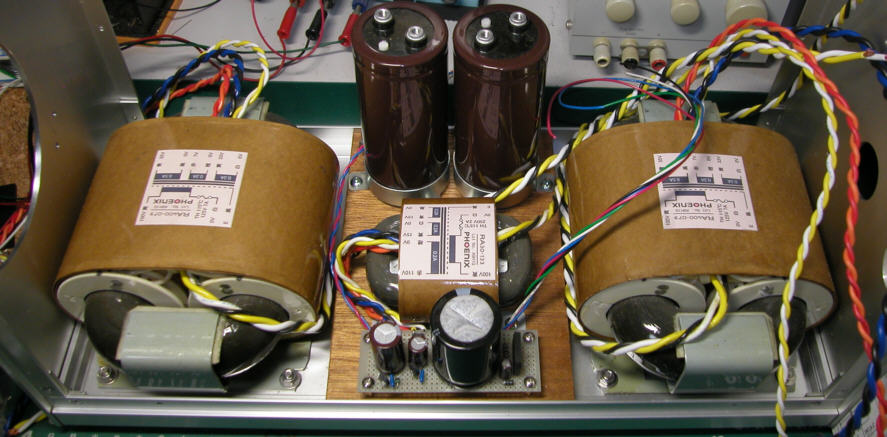

基板

|

|

|

|

|

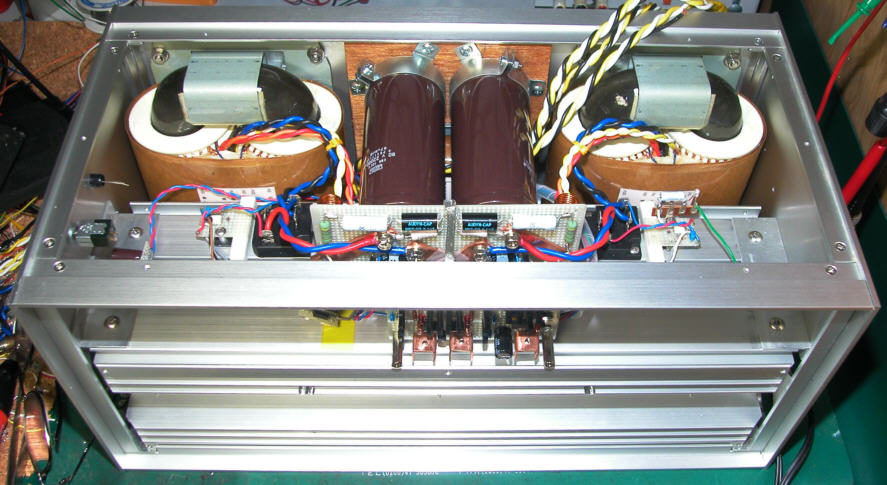

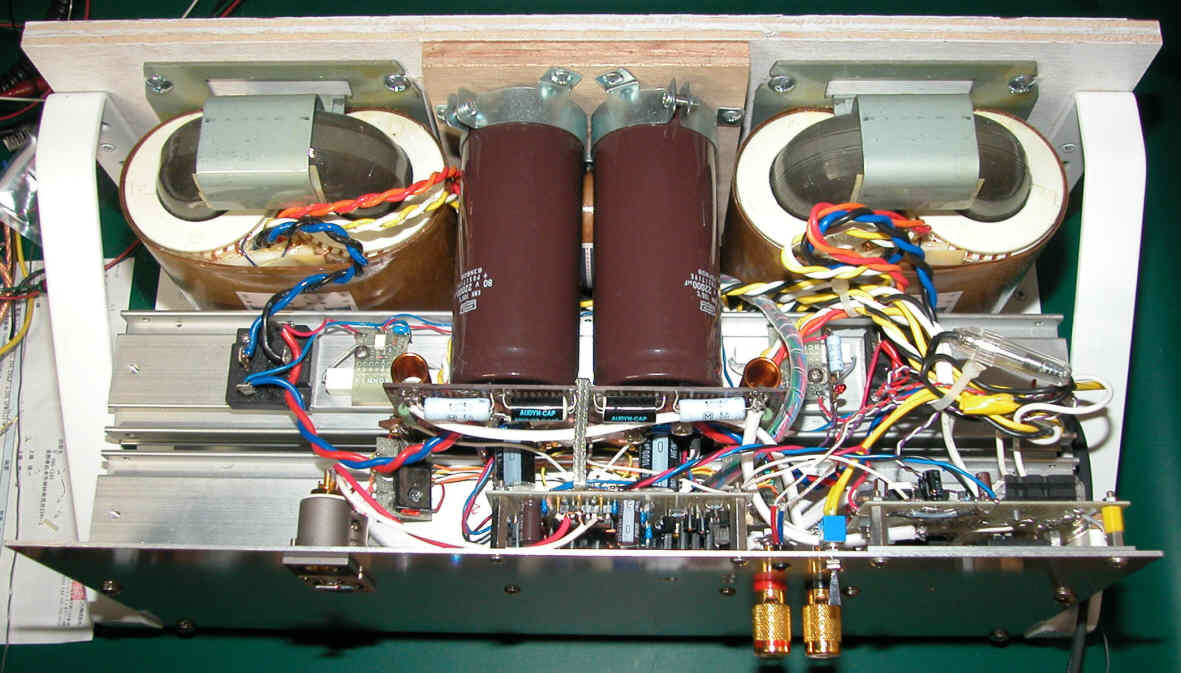

組立

Pomax(RL=8Ω,f=1kHz):240W

Gain(Unbalance Input):+23dB

THD(RL=8Ω)

f=100Hz 1W:0.00056% 10W:0.00031% 100W:0.00022%

f=1kHz 1W:0.0008% 10W:0.00036%

100W:0.00034%

f=10kHz 1W:0.0028% 10W:0.0026%

100W:0.0031%

frequency Response

1kHz:0dB 20kHz:0dB 30kHz:0.05dB 50kHz:-0.2dB 70kHz:-0.4dB

100kHz:-0.8dB

150kHz:-2.0dB

Zo=35mΩ

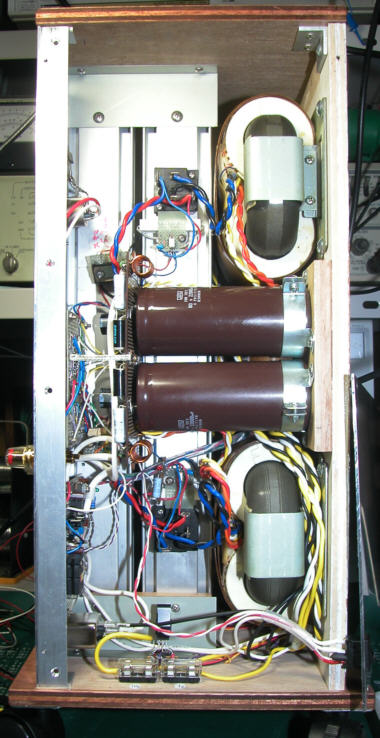

縦型に変更

|

合板L字型フレームにパーツを組み付けてフェアリングを施したネイキッドスタイルを基に、底板と天板を取り付けて縦置き型としました。 日焼け調のエイジングカラーで着色して、より一層のチープ感を演出しました。 |

|