これは符号が負ですから、主アンプと出力段の歪を打ち消す信号です。

これから、eがDaとDgを完全に打ち消す条件を考えます。

これはループゲインβKGのNFBアンプの動作に他なりません。

| Evolve power amplifiers |

| ODNF回路 | |

| ODNF回路の実験 | |

| e点の電圧波形 | |

| 雑感 | |

| 電流加算方式ODNF回路・逆立型出力段の実験 | |

| 初段加算ODNFの実験 |

「ODNF回路」とはOnly Distortion Negative Feedbackの意で、LuxmanのセパレートアンプM-7f (パワーアンプ)とC-7f (プリアンプ)に使われている回路方式です。MJ誌2000年11月号に柴崎功氏による解説が載っていますので参考にしてください。

私は当初、ODNF回路は歪打ち消し作用をしてないと思いながらも、実験してみると負帰還量を後述する1/AGに設定した場合に歪みが減少したため、この方式を歪み打ち消し作用のある回路のように錯覚していました。

私の重大な間違いは、錯覚した歪打ち消し作用と辻褄合わせをするために、回路動作の客観的事実を違えて、自分の都合のいいように解釈したことです。人の解釈がどうであろうと回路は自然の法則に従って動作しているので、回路と向き合い自然に習って行くことを忘れてはならないと肝に銘じました。

ODNF回路を動作原理に従って計算すると、動作は普通のNFBであり、DNFBやZDRのように歪を完全にゼロに打ち消しできる回路ではないことを証明できます。

下図のようにODNF回路の基本構成は、無帰還動作の主アンプAと、主アンプと並列にNFB動作する副アンプKと、主アンプと副アンプの出力を加算する部分と、その加算した信号を電力増幅する出力段Gと、出力段の出力信号を分圧して副アンプの反転入力側に返す帰還回路βから成り立っています。

|

主アンプのゲインをA、副アンプのゲインをK、出力段のゲインをG、帰還回路の帰還率をβ、入力電圧をVin、出力電圧をVo、副アンプの出力電圧をe、主アンプで加わる歪をDa、出力段で加わる歪をDgとします。 |

| β=1/AG即ちAGβ=1ならば1式と2式から3式のように、eは信号成分(Vin)を含まない歪成分だけとなります。 これは符号が負ですから、主アンプと出力段の歪を打ち消す信号です。 これから、eがDaとDgを完全に打ち消す条件を考えます。 |

|

| 2式と3式から求めたVoの歪成分を完全に打ち消し0にするためには、βKGを無限に大きくしなければならないという結論に達します。

これはループゲインβKGのNFBアンプの動作に他なりません。 |

eによって歪を相殺する動作はしてはいますが、その程度はNFBアンプと同じで、ループゲインが有限である限り、歪は残ります。

以上の数式からは、負帰還量βを1/AGに設定した場合に歪みが減少する理由が見つかりません。

また、eによる歪の相殺と、β=1/AGに設定して歪みが減ることの関係も無さそうです。

では負帰還量を1/AGに設定すると歪みが減少する理由は何か、恐らく副アンプで発生する歪が鍵になっていると思います。

副アンプがスルーレートの影響などで信号振幅が大きくなるほど歪が増加する場合、eが信号成分を含まない歪成分だけになると、副アンプが扱う信号の振幅が最も少ない状態になるため、副アンプで発生する歪が最小になると考えられるからです。

つまりODNF回路とは、主アンプに信号成分の増幅を任せて副アンプの歪を減らし、アンプ全体の歪を副アンプの大きなゲインで押さえ込むという巧みなコンビネーションプレーで、NFBの効果を最大限に活用する方式であると認識しました。

これ以降の文章は勘違いして歪打消し作用の幻想に酔っていた時の記録ですので、そのつもりで読んでください。ただし回路とデータは幻想ではなく現実のものです。

| BACK TO TOP |

取り敢えず実験してみようと考えて、以前別の実験に使った回路に手を加え下図の回路を組み立てました。

|

Luxmanの回路は上が主アンプで、下が副アンプになってますが、この実験回路では下が主アンプで、上が副アンプです。

主アンプ部分はPchデュアルJ-FET

Q2による作動回路で、ソース側には電流帰還抵抗(100Ω×2)を入れてあり、ドレイン側はQ4によるカレントミラープッシュプル回路で、その出力電流の進行方向をQ6のフォールデッドカスコード回路で上側に向け、Q7,Q8の出力段バイアス回路を通して、その上の主アンプ部負荷抵抗(4.7kΩ)に出力電圧を発生させます。主アンプのゲインは主アンプ部負荷抵抗とQ2の電流帰還抵抗+Q2のソース内部抵抗の比となります。

Q13はQ6のバイアス電流を調整する定電流回路で、VR1で主アンプ部負荷抵抗の直流電圧を調整してe点の電圧を+側電源電圧より5V程度低い電圧に設定しました。

出力段はQ7,Q8が出力段のバイアス回路で、Q9,Q10はエミッタフォロワのプリドライブ段、Q11,Q12がMOS-FETによるソースフォロワ出力段です。VR3でQ11,Q12のアイドリングリング電流を0.3Aに設定しました。

副アンプはNchデュアルJ-FET

Q1による作動回路であり、−入力側にはOUTからの帰還電圧を与え、その量はVR2で可変できるようにしました。ドレイン側はQ3によるカレントミラープッシュプル回路で、その電圧出力をQ5のエミッタフォロワで受けて、主アンプ部負荷抵抗に加えるようにしました。

ODNF回路の条件に合った歪打消し動作をしてる場合、e点に発生する副アンプ部の出力電圧は歪成分だけになるので、オシロスコープでe点のAC電圧波形を観測して、これが最小となるようにVR2を調整すると、原理的には出力インピーダンスが0になり、歪み率最小となります。オシロスコープがなければ、出力インピーダンスが0になるようにVR2を調整してもOKです。

この回路の性能ですが、負荷抵抗8Ω、出力1Wの時の歪率は、100Hzで0.0046%、1kHzで0.0046%、10kHzで0.0068%と低歪みでした。出力インピーダンスは0、残留ノイズは80μVと低く優秀です。

容量負荷安定性は、0.1μF以上ではリンギングがでるものの発振はしませんが、0.001μFで発振します。

最大出力は電源電圧が+−20Vと低いことと、+側はe点の電圧でクリップして波形が崩れるため、大きな出力は得られませんでした。

実験的に製作したので電源電圧を+20V/−20Vとしていますが、Q1,Q2の部分をカスコード回路に変更することで、電源電圧を高くできます。また出力段は前段電源よりも10V以上低い別電源とするべきです。

| BACK TO TOP |

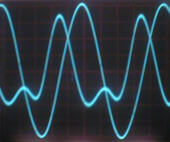

e点に発生する逆歪電圧をオシロスコープで観測して見ました。逆歪電圧の裏返しはアンプ内で発生する歪と考えられます。

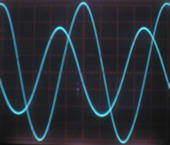

振幅の大きい方は出力電圧波形で、小さい方がe点の電圧波形です。

| 測定条件 | 波形写真 | 所見 |

| 周波数1kHz 負荷8Ω 出力1W 出力電圧波形の縦軸 1V/div e点の電圧波形の縦軸 10mV/div e点の電圧波形はACモードで測定 100Hz 8Ω負荷 1W出力時の波形も |

|

8Vp-pの出力電圧振幅に対してe点の電圧振幅は20mVp-pと小さく、出力電圧の−の振幅を増やし、+の振幅を減らすように逆歪電圧が発生しています。

|

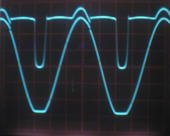

| 周波数10kHz 負荷8Ω 出力1W 出力電圧波形の縦軸 1V/div e点の電圧波形の縦軸 10mV/div e点の電圧波形はACモードで測定 |

|

10kHzでは主アンプと副アンプに位相のズレが発生して、しかも+と−ではズレ方が違っているようです。 |

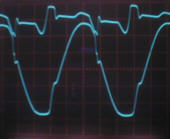

| 周波数100kHz 負荷8Ω 出力1W 出力電圧波形の縦軸 1V/div e点の電圧波形の縦軸 1V/div e点の電圧波形はACモードで測定 |

|

100kHzともなると、逆歪電圧の振幅は5Vp-pにもなります。 |

| 周波数1kHz 負荷8Ω 出力クリップ 出力電圧波形の縦軸 5V/div e点の電圧波形の縦軸 5V/div e点の電圧波形はDCモードで測定 |

|

出力電圧のクリップは−側が14Vで頭打ちになるのに対して、+側は下降スロープにスパイク波形が発生します。 |

| 周波数100kHz 負荷8Ω 出力クリップ 出力電圧波形の縦軸 5V/div e点の電圧波形の縦軸 5V/div e点の電圧波形はDCモードで測定 |

|

100kHzはクリップでは、出力電圧の歪みに逆歪電圧が追いつかないという状態です。 |

| BACK TO TOP |

このアンプではe点のAC電圧を最小にしたVR2の調整位置と、出力電圧の歪みが最小となるVR2の調整位置が一致しません。

e点のAC電圧を最小にしたVR2の調整位置では出力インピーダンスが0となりますが、出力電圧の歪みが最小となるVR2の調整位置では出力インピーダンスが僅かですがあります。

これは副アンプに歪があるため、e点に発生する逆歪み信号に副アンプの歪が加わり、正しい逆歪み信号ではなくなっていることが原因で、出力電圧の歪みを最小に調整した場合は、副アンプで歪む分を補正するように逆歪み信号を歪ませる操作をしたと考えられ、理想的な動作条件から外れた調整状態になっていると考えます。

出力インピーダンスが0となるVR2の調整位置と、出力電圧の歪みが最小となるVR2の調整位置のズレが少ない程、副アンプの歪が少ないと考えられます。

この副アンプの歪みを減らすには、更に副アンプにも歪を打ち消す副アンプを付け、そのまた副アンプにも副アンプを付けと、幾重にも続けるのか、そうした方法に頼らず副アンプを歪みを減らそうとするなら、その歪みの少ない副アンプを主アンプに据えてもいいじゃないかと矛盾が生じ、どちらに行っても出口の無い世界に閉じ込められそうです。

歪みにだけ拘っているとそうなるので、歪以外のことで何かないかと考えてみました。たとえば副アンプの周波数特性をDCにだけ作用するようにしたら、単なるDCサーボとなって副アンプの作用しないオーディオ帯域は主アンプの無帰還動作の特性になりそうです。或いは低域まで副アンプの作用をさせれば、ダンピングの効いた低域と抜けのいい中高域の音が両立できるかも知れません。

主アンプは元気はいいがほっとくと危ない新米刑事で、副アンプがそれを型にはめて諌める没個性な刑事課長という役柄に例えられるだろうか、無帰還アンプのしなやかで自由な闊達さと、NFBアンプの真面目で頑固な堅実さがウリのお笑いコンビでもいい。2つの個性がそれぞれに飛びぬけていて、それが互いに強調し合って1体化した場合のコンビネーションプレーは強力ではないかと考えると、一見片ちんばなLuxmanの回路も理解できます。

| BACK TO TOP |

Luxmanの回路は主アンプと副アンプの出力を電圧の状態で加算してますが、主アンプと副アンプの負荷抵抗を共通にして電流で加算することが可能ではないか考えて実験してみました。

前回の実験回路よりも素子数が増えてますが、これは差動回路をコンプリメンタリー・シンメトリー構成にしたためで、より低歪みな回路になっています。また出力段に採用した逆立型は、出力段をドライブする信号電圧の振幅が小さいので高域特性の向上が期待でき、出力段以外の電源電圧は15Vで動作します。

基本構成は下図のように主アンプと出力段が反転アンプであるため、副アンプは反転入力側に信号入力を与え、非反転入力側に出力からの帰還信号を与えます。

|

実験回路を以下に示します。

|

|||||

| Q1a,Q1b,Q3a,Q3b | 2SK389(GR) | Q7,Q9 | 2SA1360 | Q13 | 2SC4793 |

| Q2a,Q2b,Q4a,Q4b | 2SJ109(GR) | Q8,Q10 | 2SC3423 | Q14 | 2SA1837 |

| Q5a,Q5b | 2SA1349 | Q11 | 2SC2856 | Q15 | 2SK1529 |

| Q6a,Q6b | 2SC3381 | Q12 | 2SA1191 | Q16 | 2SJ200 |

Q1,Q2が主アンプでQ3,Q4が副アンプです。それぞれの位相の同じドレイン同士を並列接続してドレイン電流で加算しました。この加算したドレイン電流はQ5,Q6のカレントミラープッシュプル回路によってQ9,Q10のフォールデッドカスコード回路に伝え、Q11,Q12の出力段バイアス回路のエミッタに接続してある10kΩに流れます。この10kΩは主アンプと副アンプの共通負荷抵抗になっています。

Q7,Q8はQ9,Q11,Q12,Q10にバイアス電流を与える約15mAの定電流回路です。

Q13,Q14は出力段をドライブするためのエミッタフォロワ回路です。Q13,Q14のエミッタ間電圧はQ11,Q12によって定電圧化してあり、その電圧はVR2で可変できるようにしてあります。

Q15,Q16が出力段のパワーMOS-FETで、逆立型であるためソースは接地して、ドレイン電源の中性点から出力を取り出します。この出力点に主アンプと副アンプの共通負荷抵抗を接続してあるため、出力段には100%の負帰還が作用して、出力段のゲインは1となっています。

主アンプと副アンプの共通負荷抵抗10kΩと、副アンプの帰還抵抗2kΩには、発振防止のため小容量のコンデンサーを並列接続しました。

調整は、VR2で出力段のパワーMOS-FETのドレイン電流を0.5Aに設定し、VR1で歪を最小にします。出力のDCオフセットの調整回路は省きましたが、大きい場合はQ3,Q4の選別で追い込みます。

スポット的に測定した歪率のデータですが以下の通りです。

|

Po |

1W | 10W |

| 100Hz | 0.0003% | 0.0012% |

| 1kHz | 0.00035% | 0.0013% |

| 10kHz | 0.00107% | 0.0031% |

1kHzと100Hzの歪率は恐ろしいほど小さく、歪率計の波形を見ても歪成分は残留ノイズに埋もれて見えない状態で、残留ノイズ自体も36μVと小さい値です。電源ON/OFF時のショックノイズは殆ど発生しません。

この回路ではどういうわけか、VR1のどの位置でも出力インピーダンスが負になりません。

最適な歪打消し状態では副アンプのドレイン電流の信号成分が最小になるはずですが、この回路では測定しようがないので、VR1の調整は歪率の最小ポイントに設定しました。

実際に歪打消し動作しているのか、何とかして副アンプのドレイン電流の信号成分が最小になることを確認する方法はないかと考えていたら、アイデアが閃きました。俺って天才!

コンプリメンタリー・シンメトリー構成の差動回路は上下の片方だけでも動作するので、片方を電流チェックに利用することを考えました。

|

上図では上側の差動回路を電流チェックに使うようになっています。

Q1とQ3のドレインをカレントミラー回路から外して、副アンプのQ3のドレイン電流をチェックできるように電流検出抵抗を入れ、チェック端子+Ch,-Chを設けました。電流検出抵抗は500Ω〜1kΩが適当です。他は変更してません。

+Chまたは-Chの電圧をオシロスコープで観測すると、VR1の調整で波形が一直線になり、この状態で歪率最小となっているので、歪打消し動作が行われていることの確認ができたと思っています。

| BACK TO TOP |

オリジナルのODNF回路は歪打消し信号を出力段の手前で加算してますが、これを初段の入力信号と同レベルの所で加算すれば副アンプの出力レベルは最も小さくできるため、副アンプの動作振幅が小さくなり副アンプの歪が減ると考えました。

実験回路を下図に示します。

|

|||

| Q1:2SK389 | Q4:2SC3381 | Q7:2SC2856 | Q10:2SA1837 |

| Q2:2SJ109 | Q5:2SC1775A | Q8:2SA1191 | Q11:2SK1529 |

| Q3:2SA1349 | Q6:2SA872A | Q9:2SC4793 | Q12:2SJ200 |

回路構成は初段にバイポーラトランジスターを使用し、出力段にMOS-FETの逆立型を使った1段増幅回路です。

Q1A,Q2Aが主アンプで、Q1B,Q2Bが副アンプとなっていて、副アンプの出力を主アンプのエミッタ抵抗に電圧加算しています。

副アンプのエミッタで入力信号と出力信号を比較していますから、副アンプのエミッタに発生する入力信号成分は歪のない状態でなければなりません。

この回路では副アンプの入力信号を主アンプのエミッタを介して与えているので、副アンプのベース-エミッタ間の非直線で発生する歪と逆パターンの歪が主アンプのベース-エミッタ間の非直線で発生するため、互いの歪が相殺して副アンプのエミッタに歪のない入力信号成分が発生します。

帰還抵抗にCを抱かせて位相補償しないと発振します。

また100kHz方形波の形を整えるためQ1B,Q2Bのコレクタアース間にCRの直列回路を入れました。

VR1で歪率を最小に調整し、VR2でアイドリング電流を0.5Aに調整しました。

調整後のVR1の抵抗値は117Ωでした。その時の歪率のデータを下表に示します。

|

Po |

1W | 10W |

| 100Hz | 0.0010% | 0.0027% |

| 1kHz | 0.0018% | 0.0027% |

| 10kHz | 0.0056% | 0.0045% |

歪成分は第2高調波で、原因はQ1とQ2のHFEが揃っていないためと考えられます。Q1とQ2は無選別で使用したため出力に約+0.5VのDC電圧を発生しています。出力インピーダンスは0.0台で負荷のON-OFFでは正確に読み取れない小さい値です。

| BACK TO TOP |

おまけ 純粋無帰還回路