| Evolve power amplifiers |

|

改造レポート |

|

組立レポートはこちら

僅かな回路の変更でできる簡単な改造をしてみました。

改造は自己責任で、改造後は測定器による動作の確認が必須です。

★ 回路図

アンプ回路

電源回路

★ 改造箇所

出力インピーダンスを下げるため、出力段カソードから初段カソードに電流正帰還を施しました。

具体的には、基板の出力段カソードバイパスコンデンサのアース側の配線パターンをカットして、電線で初段カソード側のNFB抵抗3.3Ωに接続しました。

この 回路変更に伴い負荷変動による動作の安定性を確保するために部品定数を変更をしました。

初段入力コンデンサ0.1μFを取り外して直結にし、取り外した0.1μFを初段と出力段間のカップリングコンデンサと並列にするため、表裏対向並列接続の技で基板裏から向かい合わせに取り付けました。

初段カソードバイパスコンデンサを100μFから4.7μFに交換して、余った100μFは出力段カソードバイパスコンデンサと表裏対向並列接続

しました。

この4.7μFにポリエステルフィルムコンデンサを使いましたが、電解コンデンサでも構いません。4.7μFより容量が大きいと低域にピークができて最悪発振する可能性があります。

初段プレート負荷抵抗を470kΩに変更し、初段の電源フィルタ回路は使わず、出力段プレート電源側へ電線で接続しました。

よって初段電源フィルタ回路の15kΩ/22μFは不要なので取り外しました。

出力段プレートから初段プレートへPG帰還抵抗820kΩ追加しました。

出力段グリッド抵抗を330kΩから470kΩへ変更しました。

位相補償コンデンサ200pFを82pF+180Ωに交換しました。

PG帰還抵抗820kΩと並列に5pF追加しました。

出力からのNFB抵抗120Ωを100Ωに変更しました。

電源リップルを減らすため初段電源フィルタ回路から取り外した22μFをMOS-FETゲート側に取り付けました。

MOS-FETのゲート保護ダイオードは、ゲート側22μFの方に接続を変更する必要があるため、基板裏からの取り付けとしました。

MOS-FETの発振防止抵抗1kΩを基板のゲートのベースピンを抜いて、ベースピンの代わりとして取り付けました。

チャンネル間のクロストーク改善のため、入力側の2芯シールド線の片チャンネルをアースとして使うように接続を変更しました。

よって、2系統あった入力は1つだけとなりましたので、入力セレクタスイッチを入力のON-OFFスイッチとして使えるようにしました。

NFBの2芯シールド線はフラットリボンケーブルをばらして作ったツイストペア線に交換し、出力端子から直にLRのアースラインを独立して配線しました。

スクリーングリッド電源フィルタ回路の抵抗3.3kΩをツェナーダイオードに取り替えました。

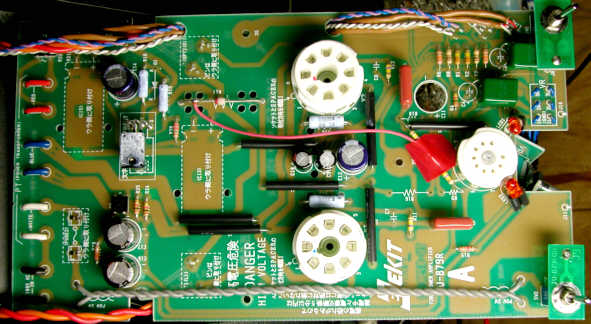

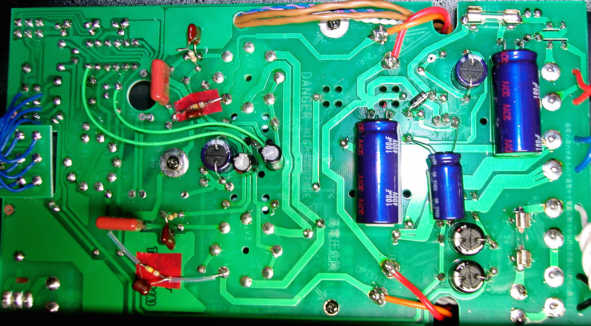

基板表面

MOS-FETが白いのは熱伝導を良くするシリコングリスを塗布してあるためです。

基板裏面

PG帰還抵抗と位相補償素子は基板裏面からの取付けです。

MOS-FETゲート側22μFも基板裏面に寝かせて、食品トレイの発泡スチロールを短冊に切ったものをクッションにして両面テープで固定してあります。

リアパネルの配線

NFBの配線はLR独立なので、GNDのスズメッキ線は不要です。

★ 特性データ

このデータはあくまでも私が組み立てた1台の特性であって、全てを代表する 特性でないことをお断わりしておきます。

■入出力特性

1kHz正弦波信号、8Ω抵抗負荷、ボリューム最大でRchを測定

オシロスコープで観測すると、出力波形のクリップが6Wを越えた位から始まり、入力0.6Vで出力8Wに達します。

スクリーングリッド電源の抵抗をツェナーダイオードに替えたことで、大出力時にスクリーングリッド電圧の低下が少なくて、クリッピングポイントが高くなったようです。

出力からのNFB抵抗120Ωを100Ωに変更したことで、ゲインが少し低くなりました。

■周波数特性

正弦波信号、8Ω抵抗負荷、ボリューム最大でRchを測定

1kHz,1V出力を0dBとしています。

改良前より低域がダラ下がりですが、改良前は低域カットオフ周波数直前に隠れたピークがあったので、それが無くなり素直な特性になっています。

高域は容量負荷の安定性と方形波のオーバーシュートを位相補償コンデンサで調整した結果の特性です。

82pF+180Ωの82pFを減らすと0.1μF以上の容量負荷で発振、PG帰還抵抗と並列の5pFを減らすと方形波のオーバーシュートが大きくなります。

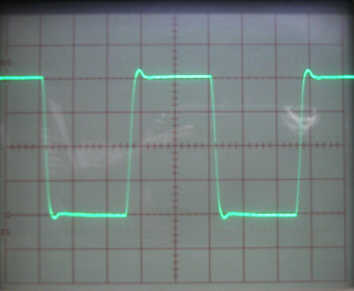

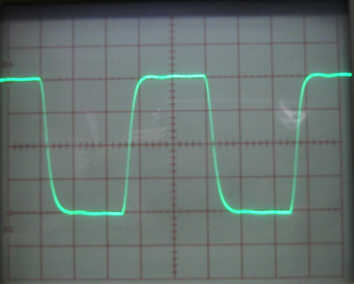

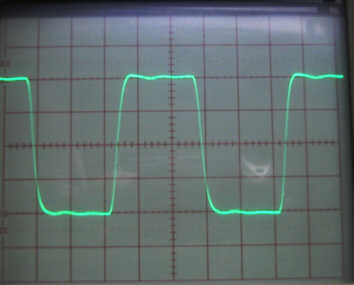

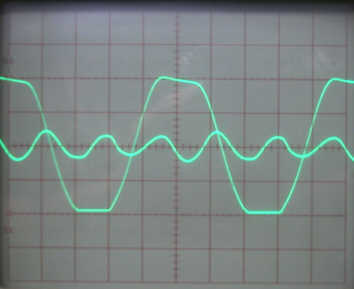

下の写真は10kHz方形波の出力電圧波形です。

無負荷 (V: 0.5V/div)

8Ω抵抗負荷 (V: 0.5V/div)

0.1μF容量負荷 (V: 1V/div)

8Ω抵抗と0.1μF容量の並列負荷 (V: 0.5V/div)

■歪率特性

8Ω抵抗負荷、ボリューム最大でRchを測定

P-G帰還量を調整して歪率を下げることができました。

P-G帰還が無いと出力波形の下側が伸びて、P-G帰還を増やすと逆に上側に伸びるので、歪波形を見て適当に調整しました。

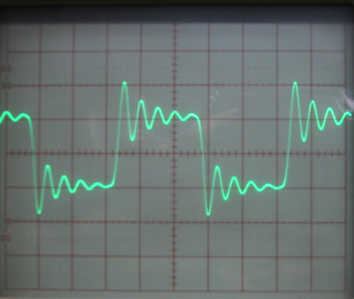

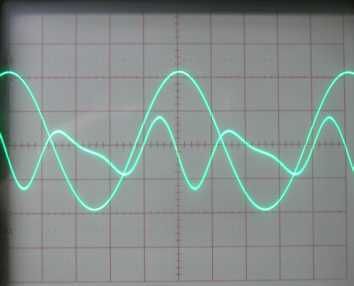

下の写真は1kHzで1Wと8Wの出力波形と歪波形です。

1kHz/1W 0.82%

1kHz/8W 12%

■出力インピーダンス特性

6〜16Ω端子を8Ω抵抗負荷電流注入法でRchを測定。

電流注入アンプの出力は1Vrms。

700Hz付近が最小値0.07Ω位、この特性を逆さにしたものがオープンループゲインの周波数特性ではないかと思います。

■クロストーク

クロストークを被る側は入力ショート、出力8Ω抵抗負荷。

与える側は8Ω抵抗負荷に3Vrms(+10dB)出力。

改造前のデータを取ってなかったので、どの程度改善されたか分かりませんが、実用には充分な特性と思います。

低域での悪化は、MOS-FETリップルフィルタの出力抵抗が数Ωと低くないからです。

3kHz位で減少しているのは逆相信号によるキャンセルが作用しているのかも知れません。

いやもしかして、出力インピーダンス特性のようにV字型になるはずが、オープンループゲインの高い帯域で12AX7のプレート間で飛付いた信号を増幅してV字型の谷を埋めているという推測の方が可能性大です。

■残留ノイズ

残留ノイズはボリューム最小、8Ω抵抗負荷で測定

Rch/160μV 34μV(JIS-A)

Lch/170μV 38μV(JIS-A)

電源リップルフィルタにコンデンサ追加した効果でノイズレベルが下がりました。

★ 最後に

![]() プリンタで印刷した手製のあごシールを貼り付け。

プリンタで印刷した手製のあごシールを貼り付け。

改造前より特性は少し良くなったけれど、音はつまらなくなったような気がします。

出力トランスのサイズがタンゴのU-608程度で低域のパワーが今一つだから、よりコアサイズの大きなものに乗せ変えたい欲求に駆られるが、出力トランスをそのままで超3極管接続にする趣向も捨てがたい、電源リップルが無いからそれには御誂え向きかも、もしかして回り道をしていた

ような。

2006/06/05