|

|

| Evolve power amplifiers |

|

|

夢か幻か20世紀の埋蔵SITがこの手に、私にはダイヤモンドにも勝る宝石。

長い

眠りの中でアンプになる時を夢見ていたんだろう。

回路に磨きを掛けてSITが最高に輝くアンプをプロデュース。

| 2SK77 MAXIMUM RATINGS (Ta=25℃ uniess otherwise nted) | |||

| Rating | Symbol | Value | Unit |

| Drain-Gate Voltage | VDGO | 200 | V |

| Gate-Source Voltage | VGSO | -40 | V |

| Drain Current | ID | 20 | A |

| Gate Current | IG | 1 | A |

| Dissipation Power (Tc=25℃) | PD | 200 | W |

| Junction Temperature | Tj | 150 | ℃ |

| Storage Temperature Range | Tstg | -55〜150 | ℃ |

実験に使い易いようにマウントベースを介して放熱器に取り付けました。

放熱シートはここで購入した[5590H] ハイパーソフト放熱材 0.5t 220×220mm 、高性能だが、はがすと破れるため1度限りの使用にしか耐えません。

放熱器はミニフライス盤で平坦に削りマウントベースと密着させました。

マウントベースは100×100×15のアルミ板をここで切断したものを購入してミニフライス盤でミーリング加工して製作しました。

実験回路1

最大出力 30W(以下全て8Ω負荷)

A=17.6倍

アイドリング電流 0.5A(バイアス電圧:22V )

歪率(1W) 1kHz:0.05% 10kHz:0.15% 100Hz:0.05%

アイドリング電流 1A

歪率(1W) 1kHz:0.05% 10kHz:0.06% 100Hz:0.05%

アイドリング電流が多いほど高域の歪が減少するから、可能な限りアイドリング電流を多く流したい。

温度によるアイドリング電流の変動は少ないようだから、電源電圧変動によるアイドリング電流の変動の対策のみで、アイドリング電流は安定しそう。

バランス出力(BTL)にすることでNチャネルSITとPチャネルSITの特性差がキャンセルされ、出力は4倍の100W以上が見込めます。

実験回路2

初段バッファをOPアンプに変更。

アイドリング電流 1A

歪率(1W) 1kHz:0.001% 10kHz:0.0035% 100Hz:0.0009%

残留ノイズ 150μV←高周波成分が多い (A)フィルタ使用で20μV

OPアンプ(OPA627) が高速で実装に気を使う。

ツェナーダイオードから発生する高周波のノイズをOSコンデンサで吸収。

カスコード接続のQ15,Q16のベースに直列抵抗(100〜1kΩ)を入れないと超高域で発振する。

容量負荷安定性が悪いため対策が必要。

帰還抵抗の抵抗値を高くすることで高域カットオフ周波数を下げて安定に出来る。

これによってDCオフセットが大きくなるため、DCバランス補正が必要になる。

アイドリング電流が1Aでは負の温度係数で熱暴走の心配はなさそう。

0.8A程度で歪率が最も低くなる。電源電圧が高い方が高域の歪が減るためBTL計画は凍結して、普通のコンプリメンタリSEPP回路で最大出力150W位を目標に方針転換する。

実験回路3

電流センサで出力段のドレイン電流を検出して一定にするサーボ回路でバイアス電圧を制御。

B級動作になるとバイアス電圧が増加してしまうため、A級動作範囲でしか使えない。

実験回路4

電源電圧変動に追随してバイアス電圧の最適値に制御するPSDCの究極形態ともいえる方法の実験。

出力段と同じアイドリング電流で動作する回路でバイアス電圧をシミュレーションして、出力段に同じバイアス電圧を与える。

バイアス電圧を数式モデルに置き換える

実験回路4の出力段のアイドリング電流Idを0.8Aに設定して、NchとPchのドレイン間電圧Vd-dを0Vから100Vまで変化させゲート間電圧Vg-gを測定して 、下図の赤色で表す曲線を得た。

この曲線のVd-d=80Vに接する直線の数式はおよそVg-g=13+0.125Vd-dである。

Vg-g=13+0.125Vd-dの13は固定分で0.125Vd-dは電源電圧に比例して変化するスライド分であり、

スライド分の係数0.125はSITのμの逆数に相当する。

直線の曲線との接点を100Vに変更するためには、固定分を上げてスライド分係数を減らす。この辺はトリマ抵抗などで実際の動作を観測しながら調整できるだろう。

このように単純に直線変化するバイアス電圧と置き換えても、Vd-d=80V付近ならばVd-dの変化に対してアイドリング電流は0.8Aに保たれる。またVd-dが80Vより高くても低くてもアイドリング電流は減少する から安全である。

実験回路5

右サイドの部分が数式モデルと同じバイアス電圧を作る回路。

JFETによる定電流回路の0.8mAをSITのバイアス回路の7.5kΩ×2に流すことで固定分の13Vを作り、SITの電源電圧Vd-dを12kΩ×2と3kΩで分圧しすることで0.125Vd-dを作り、これと同じ電圧がバイアス回路に発生するように電流変換して、定電流回路の0.8mAと加算してバイアス回路の7.5kΩ×2に流す。

実験回路6

OPA627の電源電流は7mAをバイアス電圧の固定分に充て、OPA627の電源電流にスライド分を加算する方法。

電圧増幅段の電流が増加したために、トランジスタの温度上昇で今まで無かった発振が起きるようになった。

息を吹きかけたり電源電圧を下げると発振が消えることから、温度上昇に伴って発振が始まる。

トランジスタの温度が上がるとhfeが高くなりゲインが増大することが原因だろうと、電圧増幅段の出力に220pFを追加して高域ゲインを下げるようにしたら、予測的中で安定した。

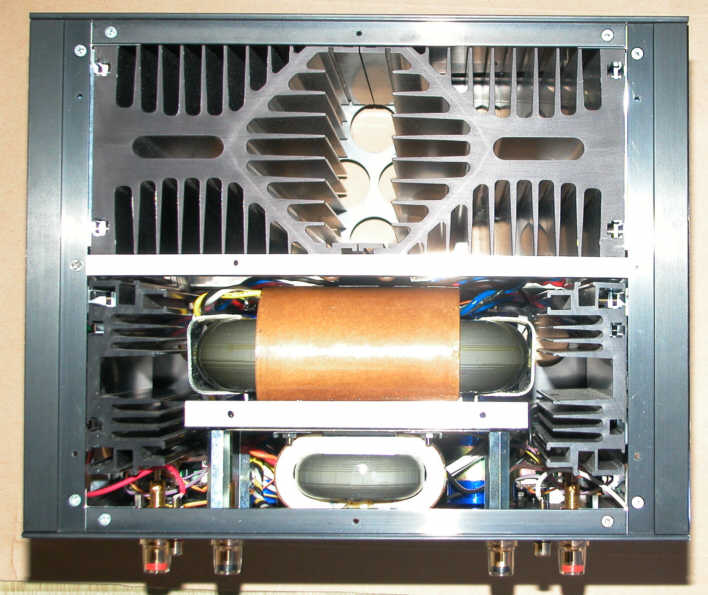

特注の電源トランスが届いたので、電源電圧に合わせて一部トランジスタを耐圧の高いものに変更した。最大出力150W

MOS-FET双方向スイッチによって、電圧増幅段の電源電圧の立ち上がりを確認してから、出力段の電源を入れる。

出力段の電源トランスの鳴きを減らすためDCサプレッサを装備した。

電源トランスの鳴きが大きいためDCサプレッサを入れたが一向に効果ないことで、いよいよ原因究明に踏み切る。

継ぎ目のないのRコアに鳴く部分などないはずだがと思い、聴診器を当ててみると案の定コアでなくコイル部分から音がするから、磁気シールドのための珪素鋼板のせいだろうことは察しが付いた。

取付け板がワニスで固着していたけど、何とか分解して絶縁紙を剥がすことができた。磁気シールドの珪素鋼板は2枚重ねで1回巻きしてあった。

磁気シールドの珪素鋼板を取り去った状態でアンプに接続してみると鳴きが止んでいる。

フェニックスのRAシリーズは標準仕様で磁気シールド付きだけど、漏洩磁束の少ないRコアトランスに磁気シールドは余計かもしれない。

漏洩磁束によるハムは部品配置に配慮すればいいが、磁気シールド板の鳴きの方は遮音とか対策が面倒になる。従って磁気シールド板なしの状態で元に戻した。

本番のヒートシンクは素子取り付け面を後加工で平面仕上げしてあるものを選びました。

SITの熱は先ず5mm厚の銅板で拡散し、SITの端子部分をクリアするための10mm厚アルミブロックを介して、ヒートシンクに放熱する。

5mm厚の銅と10mm厚アルミはここで切断したものを購入しました。精密切断は切断面がきれいです。

ケースはタカチOS199-26-33BBに組み込めるかどうかというところ。

全回路図

|

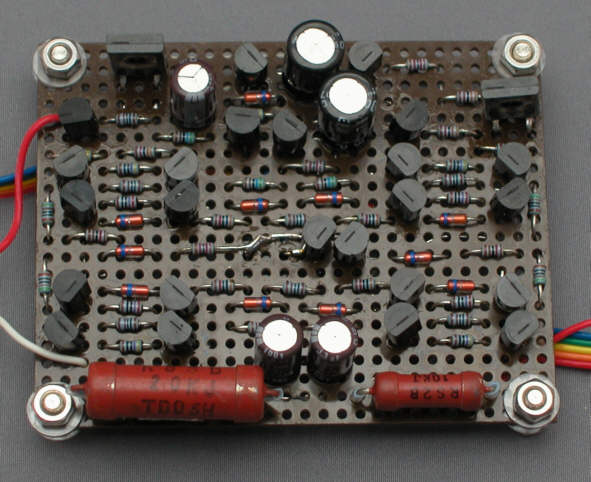

増幅回路

|

|

電源回路

|

|

MOS-FET ACスイッチ回路

|

| 保護回路

|

製作

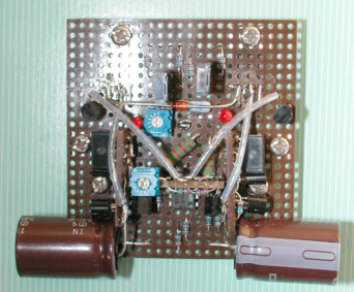

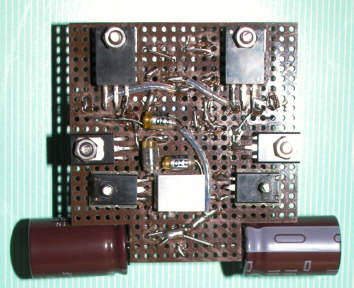

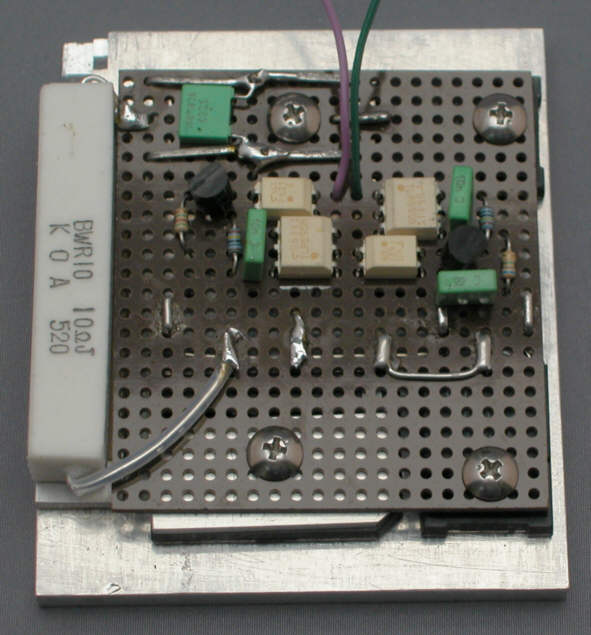

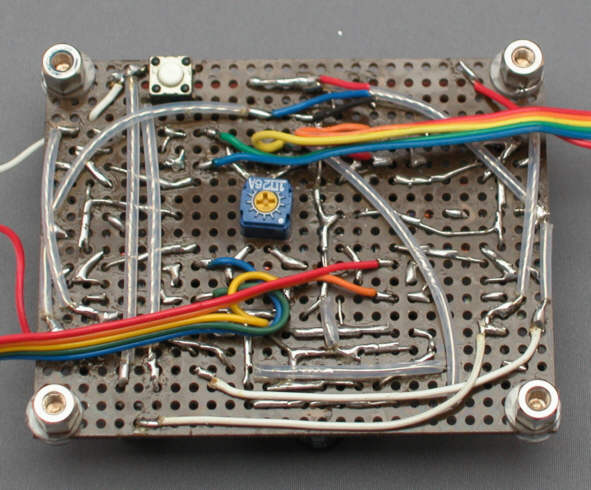

アンプ基板の表と裏

一体化して動作確認

問題あり、100kHzでフルパワー直前から不安定になる。

♪チャンチャカチャンチャン、チャチャンチャチャンチャン

動作テストは問題無しと思って100kHz入れたら、フルパワー直前に波形変形&ドレイン電流急増しました〜Shit!!

当然のことだがオペICの電流が増加することが確認されたので、オペICに電流制限回路を追加してみたが、正弦波が三角波に変形しておまけに中点電圧がずれる。

SITの入力容量をドライブする能力を高める必要があるのか、前途真っ暗。

保護回路の過電流検出が効くので実用上はOKということで取りあえずGO、今後の課題と致しましょう。

発振すると発振防止コイル1μHと並列の抵抗4.7Ωが白煙を上げ一瞬にして8Ωに。

おっと御安心を、これはドライブ段をカスコード化した時の事故で、現在の回路では大丈夫です、、多分。

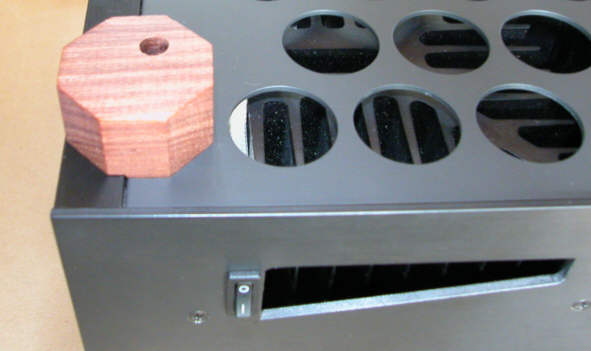

ケース加工ほぼ完了

黒アルマイトのタカチOS199-26-33BBは穴あけ加工後にスプレーブラッセン

というグラファイト塗料でマットブラックに染めました。

サイドウッドパネルをあしらうことによって、音のよさと格調の高さをイメージさせるアンプ筐体に装着変身。

側板に丁度いいサイズのブビンガ柾目板を入手。

材質が硬いため、普段はアルミ材の切断に使う電動丸鋸を用いました。

切り口が摩擦熱で多少焦げたりしましたが、まあなんとかなりました。

しかしその後のサンディングは人力ではとてもじゃないがなので、ランダムサンダーを購入。

私は機械をアシストする側へと回りました。

仕上げは初めてのオイルフィニッシュ。

ワトコオイルお試しセットを取り寄せて

、付属のパンフレットを参考に、オイルナチュラルでしっとりとした感じに期待です。

見る角度によって立体的に形が変化する効果を狙った飾りを施しました。

足の材質はチンチャンで無塗装。

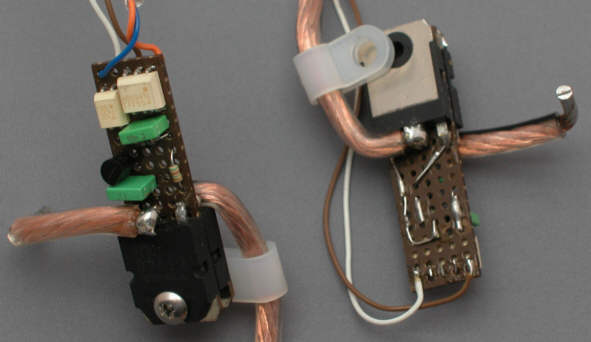

出力MOS-FETスイッチ基板

電源MOS-FETスイッチ基板

保護回路基板 裏

保護回路基板 表

一旦は組上げたけど配線が悪いのか、ハムが酷くてやり直します。

どうやら電源トランスの磁気シールドを取り去ったことによる、電源トランスからの誘導ノイズであることが判明しました。

トランスの鳴きがうるさくて外した磁気シールドだったのに、後で自分が泣きを見るとになるとは何という身の不運。

この珪素鋼板の振動は磁歪振動によるもので何かに当たってなくても板そのものが鳴くので、取り敢えず振動を抑えるため、ダクトテープを貼り付けてみました。

磁束密度に関係するのか1枚より2枚巻いた方が音が小さくなります。元々2枚しか巻いてなかったので、トタン板で同じ大きさの物を作って3枚巻きにしてみました。

ダクトテープより防振性にすぐれたダムダゲロだかアルファゲルだかに変更したがトランスのコア自体も鳴いているから、ケースを防音対策するしかない。

根本的には電源トランスを囲んでアースラインのループが出来ているためだから、磁気シールドを施しても効果は薄いことが判った。

配線を変更するしかない。最適な条件を探るためにアースラインを模したビニル電線に乗るノイズを観測しながら配置を検討した。

耳で聴く限りではトランスの鳴きの方がスピーカから出るノイズの音より大きい程度まで改善したが、未だ満足できるものではない。

ノイズレベルは(A) 0.2mVと小さくない。波形には高く鋭いパルス成分がある。

出力ノイズの波形

(L,Rの入力を1本のピンケーブルで接続して、ケーブルの引き回し位置をノイズ最小の状態にした場合)

上:Lch,下:Rch 水平2mS/DIV 垂直5mV/DIV

電源ブロックコンデンサの容量が大きいためにパルスのピークが大きいのだから、容量を減らすのも一つの対策として検討したい。

スライダックで電源電圧を徐々に上げるに連れて鳴きが大きくなるので、もっと大型の電源トランスなら鳴きが減るだろうと予想できる。

抜本的な対策としてはモノラル・コンストラクションに変更して造り直すのが最善と判断できる。