| Evolve power amplifiers |

SITパワーアンプの回路を構想する

回路案1

タムラのPP用トランスF-781は、端子に1次側2.5kΩの2つの巻線が独立して引き出されているために並列接続でき、並列接続するとインピーダンスは1/4の625オームとなります。

2次側の16Ω端子に8Ωを負荷すると1次側は312.5Ωとなるので、これでロードラインを引いて検討してみました。

SITの最大定格でゲート・ドレイン電圧は450Vで、ゲート・ソース電圧は20Vとありますが、VD-ID特性グラフの方はVD=600Vまで記載されているので、電圧に対しては相当に丈夫なのかも知れません。とはいっても高価な素子なので無茶な使い方は避けようと思います。

動作点をVD=180V、ID=50mAとして312.5Ωのロードラインを引くと、VGS=0VでVD=13V、ID=584mA、最大出力は44.6Wの計算になります。

回路は真空管でSITをアシストするハイブリッド方式です。

バランスが崩れた時にSITに大電流が流れるのを防ぐため、出力にコンデンサーを入れてDCカットします。

V3、V4によるカソードフォロワでSITをドライブします。

V3、V4のカソード・グリッド間のDC電圧レベルシフトによってQ1、Q2をフルスイングした際も、V1、V2の初段差動回路がカットオフしないようにできます。この方法は、ヤマハB-1がSITでやっていたのを真似しました。

初段差動回路に出力点のDC電圧成分だけを帰還しているため、一見オーディオ成分に対しては無帰還に見えますが、V2のプレート内部抵抗を介してV1のカソードにNFBが掛かります。

SITの内部抵抗は、この動作点の場合130Ω位であるため、完全な無帰還でもダンピングファクターは5程度になりますから、これに僅でもNFBが作用するなら

充分実用になると考えました。しかしオープンループゲインに余裕がなさそうなので、実験してみないことには分かりません。

出力トランスはV3のプレート電流が流れるので、DC重畳に耐えられる必要があります。

回路案2

V2のG2にNFBを掛ける

回路案3

回路案4

6DZ4によるP-K位相反転採用。初段はアクティブロードでゲインを高めNFBを効かせる。

回路案5

TK45F323の動作点(VDS=160V,ID=50mA)における3定数を特性図から読み取ると、およそ、

μ=23, gm=0.18S, rp=133Ωです。

TK45F323に100%D-G帰還を掛けると出力抵抗は2.7Ωとなるのでオーバーオールの負帰還は必要ないが、中性点のDC電圧を安定に保つため、オーバーオールでも負帰還を掛ける。

初段はインバーテッドダーリントン接続で直線性を改善する。

回路案6

案5の3極管を等価の抵抗に換えて、コンプリメンタリ・プッシュプル・エミッタフォロワ―でSITを強力にドライブする。

案5もそうだが、電源電圧変動でSITのドレイン電流が大きく変動するため、電源電圧を安定化しなければならない。その上、素子の温度変動に対する補償をがっちりやらなければならないだろうことを考えると、実現の難しさを感じる。

アイドリング電流はQ3のドレイン電流ID3で決まり、Q4のドレイン電流ID4、NFBが中点電圧を0Vに保つ作用によってID3と等しくなります。

ID3の変動は、この際Q3の温度特性を別にして、Q3の電源電圧VSSとQ3のゲート・ソース間電圧VGS3の変化によって発生します。

ID3の変動分は、ΔID3=ΔVSS/rD-ΔVGS3・gm

[rD:Q3のドレイン内部抵抗、gm:Q3の相互コンダクタンス]

gm=μ/rDだから、ΔID3=(ΔVSS-ΔVGS3・μ)/rD

[μ:Q3の電圧増幅率]

もし、Δ=ΔVGS3・μであればΔID3は発生しません。

R1=R2ならば、VGS3=VEE/2だから、ΔVGS3・μ=Δ・μ/2です。

従って、VEE=2VSS/μの関係が保てるよう電源を設計すれば、このアイドリング電流の変動要因を取り除くことができます。

中点電圧を0Vにするには、Q1はのベース・エミッタ間電圧VBE1をキャンセルするためのバイアス電圧VEを調整してVE=VBE1とします。

VBE1は温度特性を持っているので、VEの方もVBE1と同じ温度特性を持たせなければなりません。

Q1の負荷を定電流回路CCにするとオープンループゲインが大きくなりNFBが強力に掛かるため低歪率化、低出力インピーダンス化出来ます。

CCがQ1と同じ温度特性であれば温度による中点電圧の変動は発生しません。

初段を差動増幅に代えるとVEが省けます。その差動出力をカレントミラーを使ってプッシュプル合成するとアクティブロード同様に、オープンループゲインが大きくなりNFBが強力に掛かるため低歪率化、低出力インピーダンス化出来ます。

Q1とQ2それから、Q3とQ4の温度特性が同じであれば温度による中点電圧の変動は発生しません。

これはこれで一つの完成形と思います。

少し具体的な回路

Q6でR2端の電圧をQ8のソース電圧を基準にプルアップする。VR1(固定抵抗でも良い)でR2端の電圧を調整する。

D1,D2はCRDの耐圧(100V)オーバーを防止するための工夫。

VR2でQ8,Q9のアイドリング電流を調整する。

出力点電圧オフセットが生じても安全なように、電源アースは100Ωを介して接続する。100Ωは電解コンデンサーの漏れ電流が少なければ1kΩでもかまわない。

この回路でアイドリング電流の変動をなくすには、CC1を一定にしてCC2とCC3を、またはCC2とCC3を一定にしてCC1を、VSSの変化に連動して変化させます。

〔回路5〕差動増幅フォールデッドカスコード方式 (B)

この回路でアイドリング電流の変動をなくすには、CC1,CC2,CC3を一定にしてVBをVSSの変化に連動して変化させます。

〔回路6〕差動増幅フォールデッドカスコード方式 (C)

この回路でアイドリング電流の変動をなくすには、VB1,VB2,CC2を一定にしてCC1を、またはCC1,CC2,VB1を一定にしてVB2を、VSSの変化に連動して変化させます。

回路案5を手直しして、SITのバイアス電圧Vgsを電源電圧Vssの変動に追随して変化させSITアイドリング電流を一定にするトラッキングバイアス方式にした。

定数を算出するのに手間取ったが、これでVssの変動に追随してVgs変化させることができる。

しかし実際の場合、この回路では抵抗値の僅かな温度変化でVgsが大きく変動することが予想されるため実用にならないだろう。Veeを高くしてフォールデッドカスコードのエミッタ抵抗(3kΩ)を大きくすれば改善できる可能性はある。

回路図 第1号 ( PDF size145kB)

第1号の回路は、初段はクロスシャント差動回路の出力をカレントミラープッシュプルで合成したハイゲインアンプになっています。

その出力はSITによるSEPP出力段をドライブするエミッタフォロワに与えるわけですが、上側へはゲイン1の反転増幅器で位相反転し、下側へはツェナーダイオードでレベルシフトしたポイントから直接与えます。このようにすることで、上側のSITをマイナス方向にフルスイングすることが可能になります。

エミッタフォロワにPNPトランジスタを使い、ベース・エミッタ間電圧降下によってSITのゲート・ソース間電圧を最大+約0.6Vまでスイング出来るようにしました。SITはゲート・ソース間電圧が+0.5V以上になるとゲート電流が流れ出し、ドレイン・ソース間の飽和電圧は数V程度まで低下するため、それ以上高いゲート・ソース間電圧を加える必要はありません。またベース・エミッタ間の電圧降下は負の温度特性であるためSITの温度補償にもなります。当然ながらローインピーダンスドライブによってSITに生じるミラー容量に抗して高い周波数まで駆動でき、このドライブ方法がSITにベストマッチだろうと思います。

下側のSITのソースは-160Vであるため、下側のエミッタフォロワの電源も-160Vが基点としていますが、上側のSITのソースはSEPP回路の出力であるため、上側のエミッタフォロワの電源は、SEPP回路の出力を基点にして、出力電圧に乗って動く浮動電源でなければなりません。そこでこの回路では、出力トランスのインダクタンスで交流的に出力側とアース側をアイソレーションして、アース基点のDC電源から上側のエミッタフォロワにあるブートストラップ・コンデンサーにDC電流を供給し、ブートストラップ・コンデンサーに蓄えた電圧を上側のエミッタフォロワの電源としています。ブートストラップ・コンデンサーはSEPPの出力点からDC成分を遮断してAC成分のみを出力トランスに流す働きも(それが主なんだけどーー;)しています。

SITの電源電圧が変化した場合のアイドリング電流の変動を減らすため、ドレイン供給電圧の1/μを逆相でゲート・ソース間に与えるようにしています。その仕組みは2SA1191のベースバイアス回路にある5,6kΩと2kΩで、電源トランスの28Vを整流した電圧を約1/3に分圧して2SA1191のエミッタ側に発生させています。電源トランスの28VはSIT電源112Vの1/4であるため、2SA1191のエミッタ側にはSITの電源電圧の変動分の1/12が発生することになります。そして2SA1191エミッタ側の電圧変動分の1/2づつが上側、下側それぞれのSITのゲート・ソース間電圧の変化となりまから、SITのゲート・ソース間にはSITの電源電圧の変動分の1/24が加わり、SITのμがおよそ24であるため電源電圧が変動してもアイドリング電流は一定状態を保つことができるというわけです。

回路図 第2号 ( PDF size195kB)

第2号は初段の出力をフォールデッドカスコードでSEPP側へ伝達する方式にしました。初段のゲインが低いのでフィードバック量が少なく特性的には第1号より劣ることになると思いますが、信号経路がシンプルになっているので音質的には勝るだろうという期待があります。

クロスシャント回路の2SJ109とペアの2SJ109をフォールデッドカスコード回路のエミッタ側に定電流接続して入れることで、クロスシャント回路の2SJ109によるドリフト成分を打ち消せるようにしました。このため両方の2SJ109のドレイン・ソース間を常に等しい電圧とするべく、クロスシャント回路の方にはカスコード・ブートストラップ回路を採用しています。

SITパワーアンプの回路を実験する

ためしてガッテン トラッキングバイアス

電源電圧の変動に追随してSITのバイアス電圧を変化させる方法をトラッキングバイアスと名づけました。

実験回路を下図に示します。

TKS45F323のドレイント-ソース間電圧VDSが上昇すると、TKS45F323のドレイン内部抵抗rDのためにドレイン電流IDは増加しようとしますが、一方2SC2856がTKS45F323のゲート-ソース間電圧VGSをマイナス方向に増してIDを減少させますから、両方の作用が丁度バランスする状態ではVDDが変化してもIDは一定値を保つ筈です。

IDの変化分ΔIDは、ΔID=ΔVDS/rD-ΔVGS・μ/rDだから、ΔIDが0になる条件は、ΔVDS=ΔVGS・μです。

2SC2856はエミッタ抵抗とコレクタ抵抗が5.6kΩで等しいためゲインは-1ですから、ΔVDS=ΔVGS・μとするには、2SC2856のベース側の220kΩ/(RB+8.2kΩ)をμ-1に設定すればよいと考えられます。

TKS45F323のμはVDS=160V,ID=50mAの時に約24です。

アンプの動作点に置ける様子を見るため、VDS=160VでID=50mAとなるようにVEEを調整しておき、VDSを変化させてIDを測定したデータが下図です。

VDSに対するIDの変化はカマボコ形のカーブとなり、RBを大きくするとIDの最大点がVDSの低い方に移動します。

動作点の近傍のVDSではIDの大きな変動を防ぐことが可能ですが、広範囲で一定化することは無理です。

こうなる理由はVDSの上昇に比例してμが減少するためであると考えられます。

RBを大きめに設定しておけばVDSが高くなった場合にIDが減少するため、電源電圧の上昇でドレイン損失が過大になる危険を防止できます。

電源ドリフトキャンセル回路

トラッキングバイアスは電源電圧の変動に対してアイドリング電流を一定化できますから、電源のリップルノイズ電圧に対してもアイドリング電流を一定化できれば、電源ノイズの影響を受けない動作が可能になります。

そうするには、SITのドレイン電源電圧の変動分を検出して、その変動分を位相反転し1/μに分圧して、SITのゲート・ソース間に与える回路を考えればよいわけです。

この電源ドリフトキャンセル回路によって、ドレイン電源電圧が変動してもドレイン電流は変化しなくなるため、ドレイン電源に対してSITのドレイン内部抵抗が等価的に高くなることになります。

一方、ドレインの負荷に対しては本来の低いSITのドレイン内部抵抗で作用しますから、実に、SITに打って付けの回路方式ではないかと思います。

目がテン 温度係数

TKS45F323の温度特性を実験で簡単に調べてみたら、ゼロバイアス状態ではIDがおよそ0.2A以上から温度係数が負になり、負バイアスを掛けると温度係数が負になるIDのポイントが大きい方向に移動することが分かりました。

このため、アンプの動作点であるVDS=160V ID=50mAでは温度係数が正であるため、温度上昇と共にIDが増加して行きます。

SITが負の温度係数というのは低電圧大電流域での話で、小電流高電圧動作の場合には温度補償しないと熱暴走する危険があり得ます。

実験回路 その1

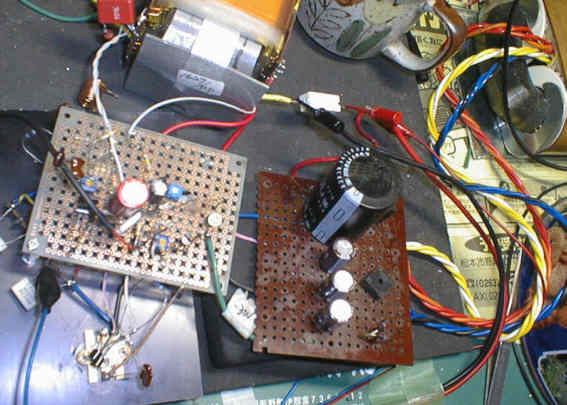

手元にある部品で上図のダブルエンドプッシュプル回路をバラック組みして動作させてみました。

出力は20W位からクリップし出しますがソフトクリップなため最大30W近くまで出ます。

出力インピーダンスは、無帰還で2.5Ω、2次巻線からNFBを掛けると0,6Ω位になります。またタムラF-781にはNF巻線があるので、そちらからNFBを掛けた場合は1.2Ω位となりました。

NFBを掛けると発振するため、初段差動アンプの負荷に100Ω+20pFを入れ、また無負荷時に発振するため22Ω+0.1μFで出力をダンプしましたが、それでもまだ10kHz方形波の波形を見るとヒゲやリンギングがあって汚いです。

PNPトランジスタによるエミッタフォロワドライブはうまく行ったようです。試しに2SA1191のエミッタと直列にシリコンダイオード1S1588を入れて、更に0.6V嵩上げした場合、出力のクリップがハードになりますが、入力電圧をもっと増すとクリップした波形にコブが発生して醜くくなります。

アイドリング電流の安定性は、温度変化に対して影響を見るため小さ目の放熱板で温度上昇し易くして実験しましたが、2SA1191をTKS45F323の上に乗せ熱結合して温度補償した効果で安定です。また電源電圧の変化に対しては、電圧増に伴ない少し上昇する程度で大きな変動にはなりません。電源投入時のドレイン電流は、立ち上がりの電圧の低い区間(VDS=15Vの時がピーク)で大きな電流(0.3Amax)になります。

■ 電源のリップルはプッシュプル動作によってキャンセルされるので、SITのペア特性が揃っていれば出力には発生しない。といってもA級動作範囲内であることが条件だが、リップルノイズが気になるのは無信号時か小音量時であるから、アイドリング電流が極端に少なくない限り問題ないだろう。

リップルや電源電圧変動はアイドリング電流の変動を招くから、これを防ぐためにトラッキングバイアスは必要である。

実験回路 その1の改

出力トランスにLundahl

LL1627/P-Pを採用し、SITにドレイン・ゲート帰還を掛けて出力インピーダンスを下げました。

EL34超3極管接続Ver.1で使った電源ドリフトキャンセル回路を取り入れました。

出力トランスLundahl LL1627/P-Pの1次側の4つのコイルは2並列2直列で使用、2次側の8つのコイルは4並列2直列で使用しました。

1次側と2次側のインピーダンス比は電圧比の実測値から計算すると、2次側8Ωの時1次側538Ωです。

調整方法はVR1をセンター、VR2とVR3を最大にして、スライダックで徐々に電源電圧を上げて行き、アイドリング電流Iaが100mAを保つようにVR3を調整しながら、VR2で電源電圧を上げ下げしてもアイドリング電流が変化しないように調整します。

VR1は出力の電源リップルノイズが最小となるように調整し、残留ノイズは70μV位になります。

アイドリング電流の安定性には難があります。

5W47kΩ(酸化金属皮膜抵抗)の温度係数が大きいため、この発熱と放熱のバランスが取れるまでアイドリング電流が一定しません。

簡単に試算してみると、5W47kΩの温度係数を100ppm(100×10-6/℃)で20℃変化した場合に抵抗値は94Ω変化し、SITのゲート電圧は0.336V変化するから、SITのgmが0.5Sとしてドレイン電流は168mAも変化してしまう

ことになります。

温度係数が25ppmの金属皮膜抵抗に代えても1/4しか変動を改善できないので、この回路は根本的に見直す必要があります。

回路は不完全ですが、出力トランスを実装テストした結果は以下の通りです。

クリップ手前の出力は60W、クリップがソフトなため80W位でも丸みがある。

20Hzでは40W位から波形が崩れはじめる。

30Hzでは60Wでも80Wでも波形の崩れは生じない。

高域は100kHzで-2.6dB落ち。

出力インピーダンスは0.8Ω。

出力トランスLundahl LL1627/P-P単体の周波数特性実測データ(1次側電圧Vp=2.72V 一定)

実験回路 その1の改の改

色々やっては見たけれど結局このような回路に落ち着くこととなりました。

まだ容量負荷で発振するので、その対策は残っていますが、残留ノイズが自己ベストを更新する26μVを達成しました。

ここまで来ると、ここまでやる必要があるのかという気持ちになるから不思議です。思い出せば、歪率を減らしたときもそうだったし、周波数特性を広げたときもそうだった。その時に初めて自分にとって必要なアンプの特性を知ることができたような気がします。

実験回路 その1の改の改の改

SITのドライブをプッシュプルにすると容量負荷時の安定性が僅かだが改善された。

この回路例に比べると性能は格段に優れているが、その分、回路は複雑化した。がしかし、それに比べて音の差は少ないだろう。

にも拘らず何故ここまでやるのか、それはこの私に、この様にしてほしいと言っているSITの声が聞こえたからだ。

その願いに応えられたことに私は満足している。

冗談じゃない、思い上がりの一人相撲はいい加減にしてくれ、俺が悲鳴を上げてのた打ち回っているというのに、という声が聞こえなくもないが、その様を見るのもまた楽しい私です。

実験中のバラックセット

浮かばれなかったその他の実験

SITをボルテージミラー回路でドライブしてみたが、最大出力のクリップ波形が気に食わないので不採用。

SEPP回路は高耐圧トランジスタに放熱器が必要になり、回路規模だけならまだしも、物量的にも大きくなる。

それで特性が良くなるなら我慢するが、DEPPとどっこいだからやる気が失せる。

この回路が一番悲惨だった。

初段にクロスシャント接続を採用、SITのソースをアース電位にする。ま、それは良いが、初段の負荷

側に定電流回路を入れて、その定電流回路の電流値を、初段の上側の電流をカレントミラーでコピーして使おうと考えた。が、それがいけなかった。なぜなら定電流回路に電流が流れなければ初段の上側の電流も発生しないからだ。「やる前に気付けよ!」