| Evolve power amplifiers |

M u g e n d y n e

亣亣亣亣亣亣亣亣亣亣亣亣亣亣亣亣亣亣丄亣 傫丠

| 儉僎儞僟僀儞偲偼 | 夞楬椺 | 尨棟傪僔儈儏儗乕僔儑儞 | ZDR偺尨棟 | OP傾儞僾偵傛傞僔儈儏儗乕僔儑儞 |

| AE偺摦嶌傪掶惓 | 惓婣娨偵傛傞ZDR | 惓婣娨夞楬偺曽幃 | ZDR夞楬椺 | D-NFB傾儞僾 |

| 儉僎儞僟僀儞傪夵傔偰峫偊傞 | 儉僎儞僟僀儞OP傾儞僾 | 丂 | 丂 |

NFB AMP

忋恾偵帵偡NFB傾儞僾偼丄

Vo=Vi/兝 偱偁傞丅

A偺僎僀儞偑柍尷偱側偄尷傝Ve偑懚嵼偟丄

Vi=Vni-Ve 偲側傞偐傜丄

Vo=乮Vni-Ve乯/兝 偲側傞丅

Vni=Vs偱偁傞偐傜

Vo=乮Vs-Ve乯/兝 偱偁傞丅

Ve 偵偼A偺榗偑娷傑傟偰偄傞偨傔丄

A偺榗偑側偔側傜側偄尷傝丄

榗偺側偄憹暆偼偱偒側偄丅

Mugendyne AMP

NFB傾儞僾偺Ve傪忋恾偵帵偡傛偆偵Vs偵壛嶼偡傞偲丄

Vi=Vs+Ve-Ve 偲側傝丄

Ve偑徚嫀偝傟偰丄

Vi=Vs 偲側傞偐傜丄

Vo=Vs/兝 偲側傞偨傔丄

榗偺側偄憹暆偑壜擻偵側傞丅

偙偺傾儞僾偺IN偲NFB娫偵偼揹埑偑敪惗偣偢丄

尒偐偗忋丄奐儖乕僾僎僀儞偑柍尷戝偵側傞偙偲偐傜丄

儉僎儞僟僀儞乮Mugendyne乯傾儞僾偲柦柤偟偨丅

Ve傪IN懁偵壛嶼偡傞偵偼丄偦偺慜抜偺夞楬傪庁傝傞偙偲偑弌棃傟偽娙扨偵弌棃偦偆偩偑丄偦偆偱側偄偲戝妡偐傝側夞楬偵側偭偰偟傑偆丅

偦偺偨傔NFB懁偱兝Vo偵-Ve傪壛嶼偟偰傕摨偠寢壥偑摼傜傟傞偺偱丄壓恾偺傛偆側夞楬傪幚尡偟傑偟偨丅

俲偺傾儞僾偼R1乣R4偵傛偭偰嵎摦憹暆婍傪宍惉偟偰偄偰丄A偺傾儞僾偺Ve傪専弌偟偰A偺傾儞僾偺-擖椡懁偵-Ve傪梌偊傞丅

俲偺傾儞僾偺弌椡揹埑Vk偼丄R6偲R3+R4偺暲楍崌惉抣Ra偲R5偱暘埑偝傟傞偺偱丄Vk=-Ve(R5+Ra)/Ra偱偁傟偽傛偄丅

幚尡夞楬

弶傔偼僨儏傾儖OP傾儞僾IC偱忋偺夞楬傪慻傫偱傒偨偺偱偡偑丄榗偑僲僀僘偵杽傟偰娤應晄擻偱偟偨偺偱丄壓恾偺僨僗僋儕乕僩偱慻傫偩榗偺戝偒偄傾儞僾傪儀乕僗偵幚尡偟偰傒傑偟偨丅

NFB AMP幚尡夞楬

偙偺傾儞僾偺摿惈偼丄弌椡掞峈 0.8兌丄丂榗棪 0.4亾乮1kHz丄8兌晧壸丄1W弌椡乯

VR100兌傪挷惍偟偰弌椡抜偺傾僀僪儕儞僌揹棳傪憹傗偡偲弌椡掞峈偲榗棪偼偙傟傛傝尭彮偟傑偡丅

壓恾偺傛偆偵OP傾儞僾IC(4558)傪巊偭偨-Ve傪壛嶼偡傞偨傔偺夞楬傪晅壛偟傑偟偨丅

偙偺晅壛夞楬傪ECA乮僄儔乕僉儍儞僙儖傾儞僾)偲偱傕柤晅偗偰偍偒傑偡丅

Mugendyne AMP幚尡夞楬

VR5k兌傪挷惍偡傞偲丄榗攇宍偺怳暆偑尭彮偟偰峴偒嵟彫揰傪夁偓傞偲埵憡偑斀揮偟偰憹壛偡傞偙偲偱丄榗懪偪徚偟嶌梡傪娤應偱偒傑偡丅

嵟彫揰偺榗棪 0.0042亾乮1kHz丄8兌晧壸丄1W弌椡乯丄丂弌椡掞峈偼 0兌偱偟偨丅

榗偑姰慡偵柍偔側傜側偄偺偼ECA偵榗偑偁傞偨傔偩偲偡傞偲丄偙偺夞楬偱榗傪姰慡偵柍偔偡偙偲偼晄壜擻偱偡丅

Ae偲Am偼揹埑惂屼揹埑尮偱偁傝丄挿曽宍偺晹暘偑惂屼揹埑傪梌偊傞懁偱丄傂偟宍偺晹暘偵弌椡揹埑偑敪惗偟傑偡丅

偙偺僨僶僀僗偼惂屼揹埑偵懳偡傞弌椡揹埑偺僎僀儞傪愝掕偡傞偙偲偑弌棃傑偡丅

弌椡掞峈偼0偱榗傕廃攇悢摿惈傕柍偄棟憐僨僶僀僗偱偡丅

Ae偺僎僀儞偼侾偱側偗傟偽側傝傑偣傫丅

Am偺僎僀儞偼0埲忋偱偁傟偽惓晧偺嬌惈傕栤偄傑偣傫丅

丂

Vin偼擖椡怣崋揹埑偱偡丅

Vd偼Am偵敪惗偡傞榗揹埑偱偡丅

Ve偲Vo偼揹埑寁偱丄Vo偼弌椡揹埑傪娤應偟丄Ve偼Ae偵敪惗偡傞揹埑傪娤應偟傑偡丅

偙偺僔儈儏儗乕僔儑儞偺夞楬偼Vin=Vo偲側傝丄Vd偼弌椡偵慡偔敪惗偟傑偣傫丅

Am偺僎僀儞傪Am偲偡傞偲丄Ve=(Vin+Vd)/Am丂偲偄偆寢壥偑僔儈儏儗乕僔儑儞偱摼傜傟傑偟偨丅

Am偑戝偒偄傎偳Ve偼彫偝偔側傝傑偡偑丄Am偑彫偝偔側傞偲Ve偑戝偒偔側傞偺偱丄Ae偺弌椡揹埑偑僋儕僢僾偟側偄尷傝丄Am偑彫偝偔側偭偰傕Vin=Vo偑曐偨傟傑偡丅

Ae傪僎僀儞侾偺傾儞僾偱偁傞僄儈僢僞僼僅儘儚夞楬偵摉偰偼傔傞偲丄壓恾偺傛偆偵抂巕偑奩摉偟傑偡丅

Am傪壓恾偺傛偆偵僩儔儞僕僗僞偵摉偰偼傔傞側傜丄僔儈儏儗乕僔儑儞偺夞楬偼僄儈僢僞僼僅儘儚傪宍惉偟偰偄傑偡丅

儉僎儞僟僀儞偲ZDR(僛儘丒僨傿僗僩乕僔儑儞丒儖乕儖)偼摨偠尨棟偱偡丅

ZDR偼擖椡偲弌椡傪斾妑偟偰傾儞僾偺敪惗偡傞岆嵎傪専弌偟丄偦偺岆嵎傪斀揮偟偰擖椡偵壛嶼偡傞偙偲偱岆嵎傪僉儍儞僙儖偡傞偲偄偆峫偊曽偲丄NFB儖乕僾偺拞偺傾儞僾偺僎僀儞傪惓婣娨偵傛偭偰柍尷戝傑偱崅傔偨傕偺偩偲偄偆峫偊曽偑偁傝丄偳偪傜偺峫偊曽傕惉棫偟傑偡丅仏

壓偵帵偡ZDR偺尨棟恾偺A偼弌椡抜夞楬偱僎僀儞侾偺揹埑僼僅儘儚偱偡丅

A偺弌椡揹棳偼戝偒偔曄壔偡傞偨傔丄A偺gm偑柍尷戝偱側偄尷傝丄A偺擖椡VX偲弌椡VOUT娫偵偼揹埑嵎偑敪惗偟丄偙傟偙偦偑擖椡怣崋揹埑VIN偲VOUT偺岆嵎偱偁傝A偺敪惗偡傞榗側傢偗偱偡丅

尨棟恾偱偼VOUT偐傜VX傪堷偒嶼偡傞偙偲偱A偺岆嵎揹埑VE傪専弌偟偰丄偦偺VE傪VIN偵媡壛嶼偟偨傕偺傪VX偲偡傞偲丄VOUT=VIN偲側傝榗偺敪惗偑柍偔側傞偙偲傪帵偟偰偄傑偡丅

VIN偲VOUT娫偵偼揹埑嵎偑柍偄偺偱丄A偼柍尷戝偺僎僀儞傪帩偭偰偄傞傛偆偵尒偊傞偙偲偐傜丄巹偼儉僎儞僟僀儞偲柤偯偗偰僎僀儞侾偺揹埑僼僅儘儚 偩偗偺棙梡偵巭傑傜側偄怴偟偄揥奐傪捛媮偟傛偆偲峫偊偰偄傑偡丅

尨棟恾偼壛嶼婍2偮巊偆傑偳傠偭偙偟偄夞楬偱偡偑丄巹偼壓恾偺傛偆偵僎僀儞1偺揹埑僼僅儘儚乮AE)偵丄VX傪婎揰偵偟偨VOUT偺揹埑乮V1乯傪擖椡偟丄VX傪婎揰偵偟偰VIN偲偺娫偵弌椡揹埑乮V2乯傪壛偊傞曽朄傪曇傒弌偟傑偟偨丅

擖椡怣崋揹埑儔僀儞偵 揹埑僼僅儘儚傪揹尮偛偲僼儘乕僥傿儞僌忬懺偱嵹偣偰偟傑偆偲偄偆丄忢幆奜傟偺柍杁偝傪寽擮偡傞斀柺丄扤傕帋傒側偐偭偨怴曽幃偱枹奐戱偺峳栰偵摜傒弌偡婥暘偵傢偔傢偔偟傑偡丅

偙偺曽幃偼擖椡偲弌椡偺堷偒嶼偩壗偩偐傫偩偲偄偭偨偙偲傪偟側偄偱丄弌椡抜偵梌偊傜傟傞擖椡揹埑傪偦偺傑傑擖椡怣崋揹埑偵壛嶼偡傞偲偄偆娙扨側傗傝曽偱偁傞偨傔丄條乆側夞楬偵墳梡偱偒傞壜擻惈 偑偁傝傑偡丅

壓恾偺傛偆偵婣娨検傪曄偊傞偙偲偱擟堄偺僎僀儞偺傾儞僾偵弌棃傑偡丅

旕斀揮憹暆

斀揮憹暆

OP傾儞僾偺儌僨儖傪巊偭偰僔儈儏儗乕僔儑儞偟偰傒傑偟偨丅

偨偩偟Spice偺OP傾儞僾偺儌僨儖偺拞偵偼丄揹尮傪僼儘乕僥傿儞僌偡傞偲OP傾儞僾偺弌椡偲愙抧娫偵戝偒側儕乕僋揹棳傪惗偠傞傕偺偑偁傝丄偦偆偟偨傕偺偼巊偊傑偣傫偺偱梊傔妋擣偡傞昁梫偑偁傝傑偡丅

儕乕僋揹棳妋擣夞楬

丂

丂

嵍偑僼儘乕僥傿儞僌偱偼巊偊側偄OPA637偱+55.82mA傕偁傝傑偡丅

塃偼崱夞巊梡偟偨AD847偱-755.03pA偲側偭偰偄傑偡丅

弌椡抜偺揹尮偼愙抧偝傟傞偺偱丄弌椡抜偵偼OPA637偺儌僨儖傕巊梡壜擻偱偡偑丄偙偺僔儈儏儗乕僔儑儞偱偼慡偰AD847傪巊梡偟傑偟偨丅

壓恾偑僔儈儏儗乕僔儑儞偟偨旕斀揮傾儞僾偺夞楬偱偡丅

榗懪徚偟偺岠壥傪尒傞偨傔偵偼夞楬帺懱偺榗偑彮側偄偺偱丄榗揹埑偲偟偰VD乮曽宍攇亇1V丄tr=tf=1兪s丄5kHz乯傪弌椡怣崋偵壛嶼偟傑偟偨丅

壓恾偼VIN偵惓尫攇1kHz丂1V傪梌偊偨帪丄VOUT偵敪惗偡傞弌椡揹埑攇宍丅

壓恾偼VIN偵曽宍攇亇1V丄tr=tf=0.1兪s丄10kHz傪梌偊偨帪丄VOUT偵敪惗偡傞弌椡揹埑攇宍丅

壓恾偼廃攇悢摿惈偲埵憡摿惈丅

壓恾偼VD偺塭嬁傪尒傞偨傔偵VIN=0偵偟偨帪偺VOUT偵敪惗偡傞弌椡揹埑攇宍丅

VD偺棫偪忋偑傝偲棫偪壓偑傝暘晹偱傂偘忬偺僲僀僘偑弌偰偄傑偡丅

偦偺傂偘偺暘晹傪奼戝偟偨傕偺偑壓恾偱丄偳偺暘晹傪奼戝偟偨偐偼帪娫栚惙傝傪尒偰偔偩偝偄丅

偙傟偼VD偺棫偪壓偑傝晹暘偺攇宍偱偁傞偨傔丄棫偪壓偑傝偺巒傔偱晧偺僗僷僀僋偑惗偠偰丄棫偪壓偑傝搑拞偼暯扲偵側傝丄壓偑傝愗偭偨強偱晧偺僗僷僀僋偑惗偠偰偄傑偡丅

偙傟偵傛偭偰VD偵媫弒側曄壔惉暘偑側偗傟偽丄VD偼弌椡偵偼尰傟側偄偙偲偑妋偐傔傜傟傑偟偨丅

偟偐偟丄偙傟偩偗尒偰傕偳偺掱搙偺岠壥偑弌偨偺偐暘偐傜側偄偺偱丄壓恾偺AD847偺旕斀揮憹暆夞楬傪僔儈儏儗乕僔儑儞偟偨摿惈偲斾妑偟偰傒傑偡丅

榗揹埑偲偟偰摨條偺VD傪壛偊偰偄傑偡丅

壓恾偼廃攇悢摿惈偲埵憡摿惈丅

埵憡曗彏僐儞僨儞僒側偟偱傕埵憡梋桾偑妋曐偝傟偰傞偺偼棳愇偱偡丅

壓恾偼VIN=0偵偟偨帪偺VOUT偵敪惗偡傞弌椡揹埑攇宍丅

VD偺棫偪忋偑傝偲棫偪壓偑傝暘晹偱弌傞傂偘忬偺僲僀僘偺怳暆偑戝偒偄偩偗偱側偔丄暯扲暘晹偺揹埑傕VD偺塭嬁偱曄壔偟偰偄傑偡丅

傂偘偺暘晹傪奼戝偟偨傕偺偑壓恾偱偡丅

丂

壓恾偼斀揮傾儞僾偺夞楬偱丄僔儈儏儗乕僔儑儞偺寢壥偼旕斀揮傾儞僾偲戝嵎偁傝傑偣傫偱偟偨丅

AE傪揹埑僼僅儘儚摦嶌偲姩堘偄偟偰丄偙偺傾僀僨傾傪夋婜揑偲巚偭偰偄傑偟偨偑丄幚偼儀乕僗愙抧摦嶌摨條偺夞楬偵亣偺晧壸傪梌偊偰僎僀儞傪亣偵偟偨偩偗偱偁傞偙偲偵婥晅偒傑偟偨丅

尰幚偵偼亣偺晧壸偼晄壜擻偱僎僀儞傪亣傕偁傝摼側偄丄奊偵昤偄偨栞偵夁偓傑偣傫偱偟偨丅

婎杮揑夞楬偼巹偑埲慜偵峫偊偨儃儖僥乕僕儈儔乕夞楬偲摨偠傕偺偱偡丅

夋婜揑偲巚偭偨傕偺偑壗偺偙偲偼柍偄婛懚偺夞楬偺暿夝庍偲偼丄巹偵偼傛偔偁傞偙偲偱偡偑丄婥晅偔偺偑抶夁偓偰偁偁抪偢偐偟偄丅

儃儖僥乕僕儈儔乕夞楬

丂

壓恾傪夵傔偰尒傞偲壗偺偙偲偼側偄丄AE偼AM偺-擖椡偲VIN娫偺揹埑傪丄AE偺僆乕僾儞儖乕僾僎僀儞攞偵憹暆偟偰AM偺+擖椡偲VIN娫偵梌偊偰偄傞偺偱丄AE偲AM偺廲楍愙懕偵夁偓側偄偲偄偆偙偲偱偡丅

巣條偵偮傑傜偸偙偲偱偍憶偑偣偟偰丄傑偙偲偵怽偟栿偁傝傑偣傫偱偟偨丅

壓恾偵帵偡傛偆偵ZDR偺尨棟傪昞偡摍壙夞楬1偼丄摍壙夞楬2偵曄宍偡傞偙偲偑弌棃傑偡丅偙偺偙偲偼悢幃偱傕徹柧偱偒傑偡丅仏

摍壙夞楬1 |

摍壙夞楬2 |

摍壙夞楬2偼擖椡怣崋揹埑偲僼傿乕僪僶僢僋偟偨弌椡怣崋揹埑偺嵎暘偵丄傾儞僾偺惓枴偺擖椡揹埑Vx傪壛嶼偟丄Vx傪壛嶼偟偨傕偺偵傑偨Vx傪壛嶼偡傞偲偄偆婣娨棪1偺惓婣娨夞楬偑丄NFB傾儞僾偺儖乕僾撪偵偁傝傑偡丅

偙偺惓婣娨嶌梡偵傛偭偰NFB傾儞僾偺儖乕僾僎僀儞偑亣偵側傞偨傔偵榗偑柍偔側傞傢偗偱偡丅

A偺僎僀儞偑亣側傜偽惓婣娨夞偺擖椡揹埑偲弌椡揹埑偺戝偒偝偼摍偟偄偱偡偑丄A偺僎僀儞偑掅偄偲丄偦偺暘偩偗惓婣娨夞偺弌椡揹埑偑戝偒偔側傝丄僩乕僞儖偺儖乕僾僎僀儞偑忢偵亣偲側傞傛偆偵摦嶌偡傞僔僗僥儉側偺偱偡丅

捈棳寢崌偱壜擻側惓婣娨夞楬偵偼師偺傕偺偑偁傝傑偡丅

僼儕僢僾僼儘僢僾宆 |

僩儔僀傾僢僋宆 |

僄儈僢僞寢崌宆 |

偙傟傜偺惓婣娨夞楬偼扨撈偱偼ON偐OFF偺忬懺偱偟偐埨掕偟傑偣傫偑丄偙傟傪NFB傾儞僾偺拞偵慻傒崬傒丄儕僯傾側斖埻偺亣僎僀儞傪棙梡偡傞強偑ZDR偺恀悜側偺偱偟傚偆丅

ZDR偺夞楬椺

僼儕僢僾僼儘僢僾宆

尨懃偱偼R1=R2丄R3=R4偱偡偑儀乕僗揹棳偺塭嬁偑偁傞偨傔丄嬐偐偵R1>R2丄R3>R4偵挷惍偡傞偲榗揹埑VD偑懪偪徚偝傟傑偡丅

弌椡抜偺傾僀僪儕儞僌揹棳偼ICC傪挷惍偡傞偙偲偱峴偊傞傑偡偑丄挷惍偼旕忢偵僋儕僥傿僇儖偱偡丅

僩儔僀傾僢僋宆

崟揷偝傫偺惢嶌婰帠偵偁傞曽幃偱偡丅

僇儗儞僩儈儔乕偺僄儈僢僞掞峈傪庢傝彍偒崅偄廃攇悢惉暘傑偱榗偺懪偪徚偟傪壜擻偵偟傑偟偨丅

尨懃R1=R2丄R3=R4偱偡偑儀乕僗揹棳偺塭嬁偑偁傞偨傔丄嬐偐偵R1>R2丄R3>R4偵挷惍偡傞偙偲偱榗揹埑VD偑懪偪徚偝傟傑偡丅

弌椡抜偺傾僀僪儕儞僌揹棳偼VB偵傛偭偰挷惍偱偒傑偡丅

IB偼VB偵僔儍儞僩儗僊儏儗乕僞傪梡偄偨応崌偵丄VB偺摦嶌揹棳傪愝掕偡傞傕偺偱丄VB偑揹埑尮偱偁傞偙偺僔儈儏儗乕僔儑儞

偱偼柍偔偰傕摦嶌偟傑偡丅

VIN偺撪晹掞峈偑R1丄R3偵娷傑傟傞偺偱

丄幚梡偵嵺偟偰偼VIN偺撪晹掞峈偑曄壔偟側偄傛偆偵丄慜抜偵弌椡僀儞僺乕僟儞僗偺掅偄僶僢僼傽傾儞僾傪捛壛偡傞昁梫偑偁傝傑偡丅

僄儈僢僞寢崌宆1

AD797傪柾偟偨夞楬偱偡丅

弌椡抜偺傾僀僪儕儞僌揹棳偼IE傪挷惍偡傞偙偲偱峴偄傑偡偑丄R1乣R4偲偺寭偹崌偄偑偁傝丄挷惍偼旕忢偵崲擄偱偡丅

偦偺偨傔壓恾偺夞楬偵曄峏偟傑偟偨丅

僄儈僢僞寢崌宆2

尨懃R1=R2+R3丄R4=R5+R6偱偡偑丄儀乕僗揹棳偺塭嬁偑偁傞偨傔丄嬐偐偵R1>R2+R3丄R4>R5+R6R1>R2偵挷惍偡傞偙偲偱榗揹埑VD偑懪偪徚偝傟傑偡丅

VB1=VB2=VB3/2偵愝掕偟傑偡丅.VB3偵傛偭偰弌椡抜偺傾僀僪儕儞僌揹棳傪挷惍偱偒傑偡丅

VIN偺撪晹掞峈偑R1丄R4偵娷傑傟傞偺偱

丄幚梡偵嵺偟偰偼VIN偺撪晹掞峈偑曄壔偟側偄傛偆偵丄慜抜偵弌椡僀儞僺乕僟儞僗偺掅偄僶僢僼傽傾儞僾傪捛壛偡傞昁梫偑偁傝傑偡丅

偙偺婡夛偵壓恾偺D-NFB傾儞僾偺夞楬傪嵞専徹偟偰傒傑偡丅

夞楬偺忋敿暘偲壓敿暘偼僾僢僔儏僾儖摦嶌偱偁傝丄怣崋惉暘偵懳偟偰偼暲楍偱偁傞偨傔丄壓恾偺摍壙夞楬偵曄姺偟傑偟偨丅

峏偵忋恾偺夞楬傪棟憐慺巕偵抲姺偊偰僔儈儏儗乕僔儑儞偟偨夞楬偑壓恾偱偡丅

弌椡偵壛嶼偟偨僲僀僘偑懪偪徚偝傟傞億僀儞僩偵R3傪挷惍偟偨応崌偵丄傾儞僾偺揹埑憹暆搙偼丄

A=Vo/Vi=1+R4/R2丂偲側傞偙偲偑妋擣偱偒傑偟偨丅

偙傟偼Q3偺僎僀儞偑0偱側偄尷傝丄Q3偺僎僀儞偺嬌惈偑偑斀揮偟偰傕惉傝棫偪傑偡丅

R3偑忋婰偺寁嶼抣偲僔儈儏儗乕僔儑儞偱摼傜傟偨抣偲偱嵎偑偁傝傑偡丅

偙傟偼僔儈儏儗乕僔儑儞偑姰慡側棟憐慺巕偱側偄偺偐傕抦傟傑偣傫丅

|

寁嶼抣 |

428.5714285714290000兌 |

| 僔儈儏儗乕僔儑儞 | 428.5711674831272499兌 |

R1=R2偲偡傟偽R3=0偲側傝傑偡偑丄偦偺忬懺偱偼Q1偺僜乕僗揹棳I3偑柍尷戝偲側傞偨傔偵旕尰幚揑偱偡丅

THD乮1W乯丂100Hz丂0.0006亾丄1倠Hz丂0.0018亾丄10倠Hz丂0.007亾

倖摿丂100倠H倸丂-0.9倓B丄150倠H倸丂-1.8倓B

僲僀僘丂0.35倣V

弌椡DC僆僼僙僢僩揹埑丂-35倣V

500兌VR偼10倠Hz偺榗棪傪嵟彫偵挷惍偡傞丅10倠Hz埲壓偺廃攇悢偱偼500兌VR偵傛傞榗棪偺曄壔偑彮側偄丅

1倠VR偱2SK1519/2SJ200偺傾僀僪儕儞僌揹棳傪0.1A偵挷惍偡傞丅10倠Hz埲壓偺廃攇悢偱偼傾僀僪儕儞僌揹棳傪0.05A偵尭傜偟偰傕榗棪偼曄傢傜側偄丅10倠Hz偱偼傾僀僪儕儞僌揹棳偑戝偒偄掱丄榗棪偑壓偑傞丅

掞峈偼5亾媺1/4W扽慺旂枌傪巊梡丅15V偼埨掕壔揹尮丅20V偼旕埨掕揹尮丅夞楬恾偵偼昤偄偰側偄偑揹尮偵偼僷僗僐儞傪擖傟傞丅

梕検晧壸偱敪怳偡傞丅僋儕僢僾偡傞偲敪怳偡傞丅

D-NFB傾儞僾偼擖椡偲弌椡偺僄儔乕暘傪専弌偡傞傾儞僾偺榗傗僲僀僘偑偦偺傑傑怣崋偵壛傢偭偰弌椡抜偱憹暆偝傟傞偐傜丄D-NFB傾儞僾偺榗傪峏偵尭傜偡偨傔偵NFB傾儞僾偺拞偵D-NFB傾儞僾傪擖傟偰傒偨偑偳偆偩傠偆丅

僆乕僶乕僆乕儖偺僎僀儞偼栺20攞丄D-NFB傾儞僾偺僎僀儞傪栺10攞偵偟偰偁傞偺偱丄愭摢偺OP傾儞僾偼2攞偺憹暆傪偡傞偩偗偩偐傜丄偦偺嵎摦擖椡揹埑偼旕忢偵彫偝偄丄偑懚嵼偡傞偙偲偼帠幚偩丅

偦偺嵎摦擖椡揹埑傪尒偐偗忋側偔偡偙偲偑儉僎儞僟僀儞偵偼偱偒傞丅

ZDR傗DNFB偼傾儞僾偺擖椡怣崋偲弌椡怣崋偺嵎傪傾儞僾偺擖椡偵壛嶼偡傞曽幃偩偑丄儉僎儞僟僀儞偼傾儞僾偺擖椡偵敪惗偡傞怣崋傪擖椡怣崋偵壛嶼偡傞曽幃偱偁傞丅

儉僎儞僟僀儞偼傾儞僾偺擖椡偵敪惗偡傞怣崋傪擖椡怣崋偵壛嶼偡傞曽幃偱偁傞偐傜丄傾儞僾偑柍婣娨側傜僎僀儞偑柍尷戝偵側傝巊偄暔偵側傜側偄丅

偩偐傜儉僎儞僟僀儞傪嶌梡偝偣傞傾儞僾偼晧婣娨儖乕僾偺拞偵偁傞昁梫偑偁傞丅

NFB傾儞僾偺拞恎偼壗抜傕偺傾儞僾偱峔惉偝傟偰偄傞偐傜丄偦偺撪偺堦偮偵儉僎儞僟僀儞傪嶌梡偝偣傟偽傛偄丅

埥偄偼儉僎儞僟僀儞傪嶌梡偝偣偨傾儞僾偺夞楬僽儘僢僋傪慻傒崬傓偩偗偱傛偄丅

偦偙偱斈梡惈偑偁傝OP傾儞僾偺傛偆偵埖偊傞丄儉僎儞僟僀儞傪嶌梡偝偣偨傾儞僾偺夞楬傪峫偊偰傒偨丅

壓恾偺夞楬偑偦傟偱偡丅

夞楬偼怓乆偲峫偊傑偟偨偑丄偙傟偼恊偟傒傗偡偄傛偆偵斈梡偺僩儔儞僕僗僞偱峔惉偟偨傕偺偱偡丅

儉僎儞僟僀儞偑嶌梡偡傞傾儞僾偼Q11,Q12偺晹暘偩偗偱丄偦傟埲奜偼儉僎儞僟僀儞偺偨傔偺夞楬偱偡丅

Q11,Q12偺擖椡怣崋偼Q7乣Q10偺揹棳偱偁傞偨傔丄偦傟傪Q1,Q2偱専弌偟偰Q3,Q4偱Q7乣Q10偺揹棳偵壛嶼偟傑偡丅

J1偼僶僀傾僗偺偨傔偺掕揹棳夞楬偱丄1k兌VR偱Q11,Q12偺傾僀僪儕儞僌揹棳傪挷惍偱偒傑偡丅

Q11偺儀乕僗揹棳偼Q9,Q8偵棳傟偰偄傞偺偱丄僇儗儞僩儈儔乕偺尨棟偱Q9,Q8偲摨偠揹棳偑Q2,Q3偵棳傟丄Q5偼掕揹棳尮偱偁傞偨傔丄Q3,Q7,Q10偼僼僅乕儖僨僢僪僇僗僐乕僪夞楬傪宍惉偟偰偄偰丄Q3偺僐儗僋僞揹棳偼斀揮偟偰Q12偺儀乕僗揹棳偵壛嶼偝傟傑偡丅

傑偨Q2,Q3偲Q1,Q4偼僋儘僗僔儍儞僩愙懕偟偰偁傞偨傔偵屳偄偺揹棳偼僔乕僜乕偺傛偆偵懳徧偵曄壔偟丄Q4偺僐儗僋僞揹棳傕懳偡傞僼僅乕儖僨僢僪僇僗僐乕僪夞楬偱斀揮偟偰Q11偺儀乕僗揹棳偵壛嶼偝傟傑偡丅

僋儘僗僔儍儞僩愙懕偺僶儔儞僗偑崅偄廃攇悢偱曵傟傞偨傔偐崅堟敪怳偑偁傝丄偲傝偁偊偢Q1,Q2偺僄儈僢僞娫偵0.1兪F傪愙懕偟偨傜埨掕偟傑偟偨丅

Q1,Q2偺儀乕僗娫傪僣僃僫乕僟僀僆乕僪摍偺掕揹埑尮偱偮側偄偱傕傛偄偱偡偑丄偦偺応崌偼掕揹埑尮偺揹埑偱Q11,Q12偺傾僀僪儕儞僌揹棳偑寛掕偝傟傑偡丅

棁偱偼弌椡偑掕傑傜側偄偺偱丄壓恾偺傛偆偵NFB傪偐偗偨夞楬偱僥僗僩偟傑偡丅

帋尡夞楬

擖椡掞峈RS偱惓婣娨検傪挷惍偟傑偡丅

RS偑彫偝偄傎偳惓婣娨検偑憹偟傑偡偐傜丄弶傔偼掞峈抣嵟戝偵偟偰偍偒傑偡丅

RS偼擖椡怣崋尮VIN偺撪晹掞峈傕娷傔偨抣偵側傝傑偡丅

敪怳杊巭偵婣娨掞峈RB偵彫梕検偺僐儞僨儞僒CN傪暲楍偵昁梫偱偡丅

RS偺挷惍偼丄晧壸掞峈RL乮100兌乯傪晅偗偨帪偲奜偟偨帪偺弌椡揹埑偵曄壔偑側偔側傞傛偆偵偡傟偽傛偄偱偡丅

峏偵偼榗棪偑嵟彫偲側傞傛偆偵挷惍偟傑偡丅

忋偺帋尡夞楬偱RS偼栺1k兌偱榗棪嵟彫偲側傝傑偟偨丅

弌椡揹埑3Vrms偺榗棪乮THD乯

RL=100兌偺応崌丄100Hz丗0.009亾丂1kHz丗0.01亾丂10kHz丗0.017亾

RL=亣偺応崌丄100Hz丗0.0003亾丂1kHz丗0.00036亾丂10kHz丗0.0012亾

偦偺屻偺幚尡偱丄Q9,Q10偺儀乕僗娫傪1000兪F偱愙懕偟偨傜丄RL=100兌丄10kHz偱傕0.01亾埲壓偵偱偒傑偟偨丅

偙偺應掕偼柍怣崋帪偺傾僀僪儕儞僌揹棳偑10倣A偱偟偨偗偳丄憹傗偣偽RL=100兌偺榗棪偼夵慞偝傟傑偡丅

RL=亣偺応崌偵僆僔儘偱榗攇宍傪尒傞偲僲僀僘偩偗偟偐尒偊傑偣傫丅

屌掕掞峈偑慡晹僇乕儃儞掞峈側偺偱丄儘乕僲僀僘側嬥懏敁掞峈偵曄偊偨傜偳偆側傞偐尒偨偄偱偡丅

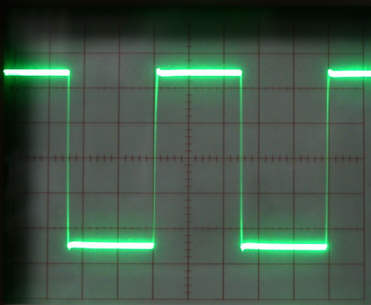

壓偺幨恀偼100kHz 10Vp-p偺曽宍攇弌椡偱偡丅

A媺嵎摦僾僢僔儏僾儖恀嬻娗僷儚乕傾儞僾

儉僎儞僟僀儞偼揹埑憹暆夞楬偑柍偔偰傕弌椡僀儞僺乕僟儞僗僛儘偺僷儚乕傾儞僾偑恀嬻娗偱偝偊傕壜擻偱偡丅

偟偐偟僔儈儏儗乕僔儑儞偱偼挷惍偑旝柇偱幚嵺偵偳偆側傞偐暘偐傝傑偣傫丅

丂

弌椡娗VT1,VT2偼掕揹棳尮Ib傪奺僾儗乕僩揹棳偵嵎摦攝暘偟丄弌椡僩儔儞僗OPT傪夘偟偰A媺僾僢僔儏僾儖摦嶌偟傑偡丅

Vb1,Vb2偼VT1,VT2偺偦傟偧傟偺僾儗乕僩丒僇僜乕僪娫偵捈棳揹埵傪梌偊傞偨傔偺揹尮偱偡丅

Vc偼VT1偺僌儕僢僪僶僀傾僗揹埑偱丄VT1,VT2偺柍怣崋帪僾儗乕僩揹棳傪侾丗侾偵挷惍偟傑偡丅

Ra偼惓婣娨検傪挷惍偡傞掞峈偱偡丅

Rb偼Ra偲偺斾偱僎僀儞傪掕傔傞NFB偺掞峈偱偡丅

恀嬻娗傪巊偭偰幚尡偡傞慜偵僩儔儞僕僗僞偱梊旛幚尡偟傑偟偨丅

VR50兌傪挷惍偡傞偙偲偱弌椡僀儞僺乕僟儞僗傪0偵偱偒傑偡丅

晧壸8兌偱嵟戝125倣W丄嵎摦傾儞僾側偺偱弌椡傪忋偘傞偲3師榗偑憹壛偟傑偡丅

偦傟偵廃攇悢摿惈傕埆偄偱偡丅

椢怓偱報偟偨晹暘偑偙偺傾儞僾偺梫偱丄儊價僂僗僗僩儕僢僾夞楬偲巹偑彑庤偵屇傫偱偄傑偡丅