Evolve Power Amplifiers

2SK1595 A級シングルパワーアンプの実験回路

Experiment circuit of 2SK1595 class A single ended power

amplifier

たった2石のパワーMOS-FETで構成したパワーアンプの実験回路です。

|

The

experiment circuit of this power amplifier is composed of only two MOS-FET.

Because the source follower circuit of high gm MOS-FET is 100% voltage feedback, the

output impedance is very low.

Then, I lowered the rate of the feedback of the source follower circuit, and gave the

voltage gain to the source follower circuit.

The voltage gain is 11 in the ratio of 10 Ω and 100Ω+10Ω.

The adjustment sets the voltage at both ends of 0.47Ω

to 0.47V with VR2 with the speaker removed.

The idling current becomes 1A by this. Next, set the voltage of the speaker connection

point to 0V with VR1.

The maximum output power is about 2.5W in 8Ωload. The output impedance is about 0.8Ω. |

高gm MOS-FETの持つ大きなゲインの何割かを電圧増幅に回して、その余剰ゲインだけで出力インピーダンスを下げたとしても結構実用になるアンプができるのではないかと考えました。

上段の2SK1595が電圧増幅と電流増幅を行い、下段の2SK1595は単なる定電流回路です。

両方とも放熱器に取りつける必要があります。

電源はアースから浮いた状態ですから、ステレオアンプとする場合には電源を共有にできないので、電源トランスでアイソレーションされた2組の電源が必要です。

また、スピーカーもアースには接続されていませんから、スピーカーコードに乗ってくるノイズは有害です。

電圧ゲインは10Ωと100Ω+10Ωの比で11倍です。

調整はスピーカーを外した状態でVR2で0.47Ω両端の電圧を0.47Vに設定します。

これでアイドリング電流が1Aとなります。

次にVR1でスピーカーを接続する部分の電圧を0Vに設定します。

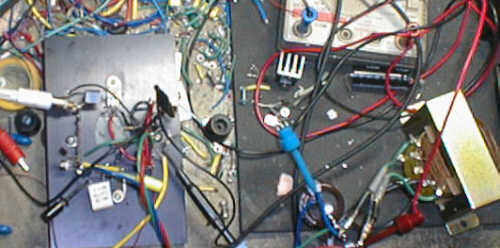

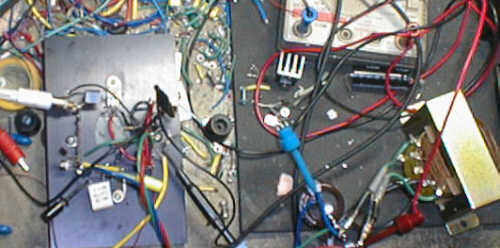

バラックセット

最大出力は8Ω負荷で2.5W程度、出力インピーダンスは約0.8Ω、従って8Ω負荷のダンピングファクターは10程度です。

10kHz方形波応答  電極間容量が大きいため波形の角が丸まる。

電極間容量が大きいため波形の角が丸まる。

この実験回路には実用レベルの性能はありませんが、いつかもっと入力容量の少ない高gmパワーMOS-FETが出現した折には実用機として実現する可能性を秘めています。

チャンネル損失の大きなパワーMOS-FETを用いて、電源電圧を上げてアイドリング電流を多くすれば、出力が増大し出力インピーダンスは低くなります。

Back to top

Copyright © 1998

Shinichi Kamijo. All rights reserved.

最終更新日:2000/04/23 11:33:25 +0900

電極間容量が大きいため波形の角が丸まる。

電極間容量が大きいため波形の角が丸まる。