金属シャシーを使用してないので電磁気的な迷電流の発生が無く、クリーンな環境であるため、自家中毒症状の音質劣化を生じません。

Evolve Power Amplifiers * Links

MOS-FETドライブ 、エミッタ抵抗レス 、無帰還

2SB600/2SD555 SEPP A級15W モノラル パワーアンプ

MJ無線と実験 1993年11月号 に発表

|

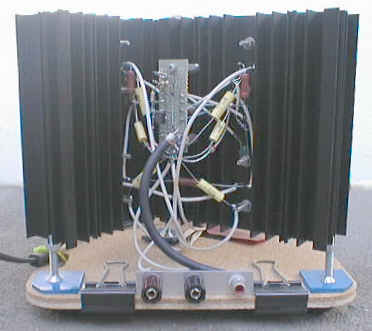

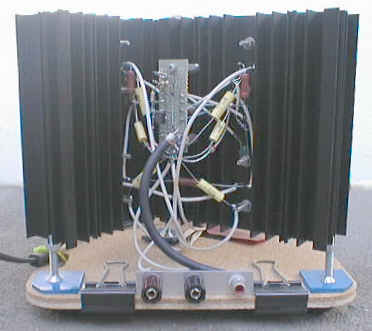

本機はご覧の通りケースに組み込まず、回路毎のブロックはコルクボードに乗せてあるだけで固定はしてません。 |

|

2枚の放熱器を支え無しで立つように、直角に組み合わせました。そして、その内側に基板を取りつけて最短の配線をしました。 |

|

ほとんどバラックセットに近い造りですが、ケースにキチッと組み込んだよりも、バラックセットの段階で音出した時の方が、常々、音の鮮度が高かったように感じていたので、敢えてこの造りにしました。 |

|

物理的振動を遮断するため、各パーツブロックの下に制振材(ソルボセイン)を敷きました。 金属シャシーを使用してないので電磁気的な迷電流の発生が無く、クリーンな環境であるため、自家中毒症状の音質劣化を生じません。 |

|

|

|

小さな基板を使い、ほとんどを空中配線して、相互干渉の無いように注意して、見栄えなど気にせず最短で接続してあります。 |

本機の特徴

最大の特徴は,終段のバイポーラトランジスターのドライブ段にパワーMOS-FETを用いて,温度特性の相殺を図り,バイアス電流を一定に保つようにして,エミッター抵抗を排除したことです.

このため,A級動作と相挨って,出カインピーダンスは極めて低くなり,オーバーオールのNFBを要せずに十分な性能を得ることができました.

エミッター抵抗を排除して新たに,アンプとスピーカーの間に介在するあらゆる物を排除しなければ,アンプはスピーカーの挙動を適確に捕らえられず,正確な駆動ができないと確信しました.そこで本機は,スピー力ーコードをできるだけ短くするために,スピーカーの近くに置くことを前提としたモノーラル構成としました.

一般的な温度補償

バイポーラトランジスターの温度特性は図1に示すように,温度上昇と共にVBEが約-2mV/℃の温度係数で低下するため,平行してバイアス電圧を下げないと,Ioが増加して発熱量が増し更にIcが増加する熱暴走で破壊します.

このために一般的なパワーアンプでは,図2のように終段のトランジスターと熱結合した温度補償素子をバイアス回路に使用し,終段トランジスターの温度変化の後を追いかけてバイアス電圧を変える方式が取られています.

この方式の受入れ難い点は,熱伝達遅れで温度補償に取り戻しできないほどの不足を発生させないように,VBEの低下によるIoの増加を緩やかにするため,エミッター抵抗を入れなければならないことです.

このエミッター抵抗によってエミッターフォロワーの出力抵抗が制限されるので,トランジスター本来の能力は失われます.

MOS-FETドライブ方式

パワーMOS-FETの温度特性は,スレッショルド電圧と順伝達コンダクタンスが温度上昇と共に低下するため,順伝達コンダクタンスの低い小電流領或ではスレッショルド電圧の温度による変化が支配的となり,逆に大電流領域では順伝達コンダクタンスに依存し,図3に示す伝達特性のようにIoが大きくなるにつれてVGSの温度係数は正から負へと変化します.

このことは,Ioの設定で任意の温度係数に調整できるということです.

図4のようにパワーMOS-FETをドライブ段に使用し,バイポーラトランジスターを終段に使用したダーリントン接続とし,IoをRsで調整して,VGSとVBEの温度による変化分が打ち消し合うようなVGSの温度係数にすると,温度変化に対してIcを一定にできます.

特にパワーMOS-FETの自己発熱でVGSの変化をさせると,他からの熱の伝達を待つ必要がないので,同時刻的,或いは先読み的な制御が可能で,そうなればエミッター抵抗を排除できます.

ただしVBEとVGSの温度による変化分を厳密に等しく維持することは難しいので,熱暴走の防止を最優先に,Icの若干の変動は容認してVGSの方がVBEより先に速く変化するようにします.

エミッター抵抗を排余するとトランジスターを並列接続できないので,大出カのアンプは無理ですが,出力素子を多数並列接続したアンプとは比較にならない質の高い出力抵抗特性が期待できます.

バイホーラトランジスター本来の出力抵抗を得るには,べ一ス側を定電圧性信号源で強力にドライブする必要がありますが,ドライブ段のパワーMOS-FETには,終段で使う場合と同程度のIoを流すため,ソース出力抵抗が低くく好都合です.

パワーMOS-FETを終段で使う場合に比べて,トランジスターのドライプ段に使う場合のメリットは,前述したバイアス電流の安定と出力抵抗の低滅の他に,VGSとIoの動作振幅が減少することと,トランジスターを定電圧ドライブすることのダブル効果で,歪みの発生が格段に減り高域特性が向上することです.本方式の特異性として,終段のトランジスターのバイアス電圧をドライブ段MOS-FETで一方的に制御するため,信号出カに伴なう終段トランジスターの発熱量の変化に対応できず,B級動作では大出力時にバイアス電流が増加して熱暴走する危険があり,一方A級動作ではバイアス電流が滅少してAB級動作に移行することが懸念されます.

このことについては前述した一般方式でも熱時定数の分の変化を免れませんが,本方式ほど極端ではないので,実用化では取り敢えず熱結合による一般方式と併用します.

終段トランジスターの動作点に関しては,Icのカットオフ付近は出力抵抗が高く,その変化も大きいので,バイアス電流の大きいA級動作が理想的です.バイアス電流の熱暴走を防止するためには,終段トランジスター接合部の温度変化をドライブ段MOS-FETチャンネルの温度変化により緩やかにします.

具体的には,終段トランジスターにコレクター損失の大きな素子を用いて,熱容量の大きな放熱器に低い熱抵抗で取り付けることです.

ただし,実験してみるとRETやEBTなどの高ftパワートランジスターは温度によるVBEの変化が速く,熱暴走しやすいために採用を見合せました.

本機の回路

|

図5 |

①電力増幅部の概要

全回路を図5に示します.実践的な観点から予備実験を重ねた結果,ドライブ段MOS-FETに最もホピュラーな2SJ49/2SK134を,終段のトランジスターは,製造打ち切りになった品種ですが,まだ入手可能な2SB600/2SD555(TO-3)形コレクター損失:200W)を採用しました.終段トランジスターのバイアス電流は,放熱器の温度と兼ね合いから約1Aとしました.また,A級動作による出力は最大15W(RL=8Ω)程度です.

②放熱器

T0-3形2石を縦並べに取り付けられるフレックスTF-1214A-2を使いました.ドライブ段FETを上側に,終段トランジスターを下側に配置すると,空気の対充効果で終段トランジスターに冷気が補給され,ドライブ段FETは終段トランジスターの熱気に温められるので,VBEの減少分よりVGSの増加分が大きくなって,パイアス電流が減少するため熱暴走が妨げます.

③電源部

トランスはタンゴA-35Sで,終段の電源は17V端子を使いDC約22Vとしました.ドライブ段の電源はMOS-FETの電極間容量の電圧依存性と飽和電圧の高さを考慮して,20V端子に5.5V巻線を継ぎ足しDC約34Vとしました.電圧増幅部の電源はドライブ段電源から取り出し,100Ω2Wの抵抗と30Vのツェナーダイオードで安定化しました.

④電圧増幅部

電圧増幅部は初段にJ-FETをゼロバイアス動作で用いたコンプリメンタリー・プッシュプル2段増幅です、電圧ゲインを規定した1段完結の増幅回路を2つ重ね合わせた方式で,各々の素子に適した使い方と,卜一タルバランスに優れた回路定数によって,高いポテンシャルが引き出せます.本機は初段にCisは小さいがgmも低い2SJ103/2SK246を採用し,バイアス電流に比べ動作電流の振幅を少なめにして,直線性の良好な特性を得る回路定数としてあります.

⑤Rsの値

バイアス電流がおよそ1Aの状態で実地判断して,バイアス電流の変動を無くすことよりも熱暴走を防ぐことを主眼に置き,温度上昇に伴なうバイアス電流の変化が僅かな滅少傾向となる3Ωとしました.ドライブ段パワーMOS-FETのIDは0.4A強となります.

⑥ドリフト対策

電圧増幅部はコンプリメンタリー素子同士の温度環境を揃えるために熱結合を行いました.電力増幅部では,2SK134よりも2SJ49の方が温度によるVGSの変化分が大きいため,その差をバイアス回路て個別に温度補償して打ち消しました.2SK134側バイアス電源のQ4,Q5を放熱器に熱結合して,バイアス電圧が温度上昇に応じて低下するようにし,一方2SJ49側バイアス電源のQ6は,Q8による温度係数が正の定電流回路によって,バイアス電圧が温度で変化しないようにしてあります.ドライブ段FETとQ4,Q5の温度補償が重複して補償過多になりそうですが,Q4,Q5の熱結合の度合が小さいことと,ドライブ段FETは温度上昇でIDが減少して温度補償効果が小さくなるので,総合的に広い温度範囲で平衡を保てます.

⑦発振防止対策

バイアス回路の熱結合のため,ドライブ段MOS-FETのゲート側配線を長く引き回すことから,ゲートと直列に100Ωを入れました.電源の高周波バイパスには0.47μFを,ドライブ段MOS-FETのドレイン,終段トランジスターのコレクター,電圧増幅部電源のツェナーダイオードの各々とアースの間に入れました.容量負荷に対する安定性を高める目的で,電圧増幅部2段目の負荷抵抗5.6kΩと並列に100pF+68Ωを入れました.68Ωは無いとクリップした時に僅かな高周波発振をします.この辺はケースバイケースで調整する必要があるかも知れません.

製作

本機は写真1~4のようにケースを使わず,コルクボードにソルポセインを敷き,電源トランス,ブロックコンデンサー,放熱器の各パーツを,固定せずに置いただけの裸の構造です.

簡単で安上がりですが,これは手抜きではなく勇気ある挑戦と自負しています.

ケース等の金属板は,電磁誘導と機械振動の変換と伝達の媒体となって音を濁らせると考えられ,経験にも,きちっとケースに納めた後より,バラックセットで試験的に聴いた時の音の方が良かったので,このようにしてみました.コルクボードはコルクに合板を貼り合わせてある220×300mmの既製品です.

これに半球形のゴム脚を付けて使いました.いずれ,このボードは省き,スピーカーボックスの上に直接アンプを並べるつもりでいます.

ソルボセインは,3mm厚のものを,カッターナイフで適当な形に切って使いました.

アンプ本体はブロックごとに分けて組み立て,電線を通してのみ,それぞれが接続されています.

電源トランスには,パワースイッチ,ヒュ一ズホルダー,LEDをLアングルに組んでから取り付け1個のブロックとしました.

さらにブロックコンデンサー4本を粘着テープで束ねて,端子に直接ブリッジダイオードを半田付けしました(図7).

図7

放熱器は自立するように2枚を直角に連結して,内角に電圧増幅部の基板を取り付け,下から空気が流入するように脚を付けました.入出力端子はLアングルに取り付けて,事務用クリップでコルクポードに止めました.

放熱器に基板を取り付けるため,図8のように放熱器の丸溝に2mmナベ小ネジの頭を滑り込ませて,適当な位置で2mmナットを半田付けした長さ25mmのスペーサーを固定しました.

図8

基板上のトランジスタ一やFETは放熱器の対向面に取り付け,調整する抵抗の付け替えを容易にしました.

また,温度補偵用の2SA1360,2SC3423はフルモールドタイプなので,後者はパワーMOS-FETの取り付けネジに,絶縁ブッシュを兼ねて共締めしました.

この取り付けネジにはテフロンチューブを被せて,放熱器に接触しないようにしてあります(図9).

図9

基板が露出しているため風の影響でドリフトが発生しやすいので,部分的に温度係数が小さい金属被膜抵抗を使いました.その他の抵抗は酸化金属被膜抵抗です.

使用部品のほとんどはMJ誌の広告に載っていますから,入手は容易にできると思います.

ブリッジダイオードPB112FはPB102Fの後継品種で同様に使えます.

また,J-FETのlDssは2SJ103/2SK246が4~8mA,2SK117は5mA以上ならば使用可能です.

2SJ103/2SK246は,調整抵抗RT1,RT2ができるだけ低くなるように実際の回路でペア選別を行いました.

参考までに,ステレオとして2台の製作に使用したJ-FETのIDSSは表1,調整抵抗の値は表2の通りです.

2SK246より2SJ103のIDSSが相当大きいですが,2SJ103の方がgmが大きかったため,その補正用にRT1を封入しているので,I。が減少して2SK246のIDSSとほぽ等しくなりバランスが取れています.

なお,本機をコピーして製作される場合,表1と同じにIDSSを揃えても,他の多くの要因で調整抵抗は同じ値になりませんから,どうしても調整箇所は必要です.図10にアンプ部分の配線を示します.

図10

調整方法

調整作業は動作テストを兼ねて後述する順番に行いますが,事前に次の準備が必要です.

①準備段階

RT1,RT2に100Ωの,RT3,RT4に500Ωの半固定抵抗を仮接続して,RT1,RT2,RT4を最小に,RT3を最大としておきます.なお,2SJ103よりも2SK246のIDSSが大きい場合は,RT1をQ1側に,RT2をQ7側に適宜変更します.終段トランジスターのloを監視するため,電流計または電流検出抵抗(1Ω以下)を並列接続した電圧計を,2SD555のコレクター電源間に接続します.入力をアースし,出力は無負荷でオッシロスコープに接続します.

②第1段階

電源電圧をスライダックで徐々に上げ,終段トランジスターのlcが過大に流れたり,オッシロスコープに発振波形などが出ないことを確認します.異状が認められたら,すぐに電源を切り,確かな原因の究明が必要です.

③第2段階

電圧増幅部の2段目の5.6kΩと並列に内部抵抗の高い直流電圧計を接続し,この電圧を±10mV以内にRT1を調整します.これは電圧増幅部の出カを0Vにしておくための仮調整です.5.6kΩを短絡したり,内部抵抗の低い電圧計などを接続すると発振するので注意します.

③第3段階

終段トランジスターのIC(バイアス電源)を1A,出力DC電圧を0VにRT3,RT4を調整します.この調整は互いに影響し合うので,コツをつかむまで半固定抵抗を極端に動かさないことです.1時間以上通電して,バイアス電流が安定しているか,熱暴走しないかを確認します.ここまで済むと音出しが可能です.

③第4段階

歪み率を最小に,かつ出力DC電圧をOVにRT1,RT2。を調整します.本機は出力1W(RL=8Ω,f=1kHz)で歪み率最小に調整してあります.2SJ103/2SK246のペア選別はこの段階で行いました.最後に,第3,第4段階を再確認しながら,半固定抵抗を同じ抵抗値の固定抵抗に付け換えて完了です.

本機の特性

最大出力は図11の歪み率特性に見られるように,終段の電源電圧に余裕があるため,A級動作出力15W以上ではB級動作となり,そのまま上昇し続け,25Wくらいで終段トランジスターが飽和して歪み率が急上昇します.

図11

しかし,まだMOS-FETから終段トランジスターのべ一ス・エミッター間を通して電力が出力されるため,図12の入出力特性のように30W以上まで伸びてきます.

図12

出カインピーダンス特性は電流注入法による測定で,図13に周波数特性と共に示します.

音声帯域内では0.08Ωぐらいと低いのが,周波数特性に対応した変化となるのは,ドライブ段MOS-FETのソース出カインピーダンスが周波数特性と共通の原因,即ち,ドライブ段MOS-FETの入力容量の影響を受けるからです.

図13

周波数特性は,パワーMOS-FETを終段に用いた場合よりドライブ段に用いた方がゲート・ソース間に加わる信号電圧の振幅が少なく済むため,MOS-FETの入力容量で□スする信号成分が減り,その分だけ高域特性が向上しています.

温度,バイアス電流,出力DC電圧について,電源投入から1時間のデータを,図14に経時特性として示します.

図14

温度測定は放熱器のもっとも温渡が高くなる上端面中央に温度計の熱電対を取り付けて行いました.

また同時に室温も測定しました.

放熱器の温度は,およそ30分で発熱量と放熱量が平衡状態に到達し,その後の上昇は室温の上昇によるものです.

バイアス電流は過渡的なピークが電源投入から2~3分後にありますが,その量は小さく,およそ10分で安定します.

このパターンから温度補償の状態が推測できます.

本機の場合は間題はありませんが,仮に終段トランジスターの温度上昇が速くて,ドライブ段MOS-FETによる制御が間に合わないと,バイアス電流は収束へ向かわず,際限なく増加し続けて熱暴走します.

またドライブ段MOS-FETのIDが不十分な場合は,バイアス電流が一旦は収束へ向かいますが,温度上昇に伴ってIDが減少するため,MOS-FETの温度補償量が足りなくなり,再びバイアス電流が増加するパターンとなります.

温度に対しては十分安定なバイアス電流ですが,図15に示すようにAC電源を変化させると,実用には差支えありませんがバイアス電流が変動します.

図15

これはエミッター抵抗を辮余したことによる副作用で,終段のgmが高いために,電源電圧の変化でドライプ段のIDが僅かに変動しても,それが増幅されて大きなバイアス電流の変動となるからです.

この課題にはドライブ段をカスコード接続したり安定化電源とすることで対処できますが,回路を複雑化すると更にまた別の課題が出ていたちごっこになりそうなので,最小限の回路で最大限の成果を得ることに努めました.

出力DC電圧はバイアス電流と同じく,電源投入からおよそ10分で安定圏内に入ります.電源0N,0FF時のショックノイズは0.5V以下で小さく,スピーカーから出る音は僅かです.

写真5~7に1OkHz方形波応答を示します.なお,放熱器を覆うと発熱量が多いのでたちまち温度上昇します.

それでもバイアス電流は安定で熱暴走はしません.また,放熱器の最高温度は設計上100℃くらいまで許容できます.

しかし信頼性だけでなく,音質の点からも,できるだけ温度上昇は少ない方がよく,かといって直接風を当てるとドリフトが増えますので,設置場所の周囲を十分に空け,特に上部は開放して熱気がこもらないような配慮が必要です.本機の音質はスッキリと軽くて浸透力のある,ナチュラルな誇張のない音です.ありのままを再生しているという,本物であることの安心感で,音楽を聴くことに自然と没頭させてくれます.

Copyright © 1997

Shinichi Kamijo. All rights reserved.

最終更新日: 2000/11/18 10:06:33 +0900