|

丂

丂

僋儘僗僔儍儞僩擖椡丒僩儔儞僗儕僯傾僶僀傾僗

2SK3497/2SJ618

Power Amplifier

|

廬棃偐傜偺掕斣晹昳偑擖庤崲擄偵側偭偰峴偔帪戙偺棳傟偵崌傢偣偰丄尰嵼偐傜悢擭愭傑偱尰峴昳偱擖庤壜擻偱偁傠偆晹昳偱惢嶌壜擻側丄懅偺挿偄傾儞僾偺奐敪傪僥乕儅偲偟傑偟偨丅

僩儔儞僗儕僯傾僶僀傾僗偵巊偆MOS-FET偺慖暿

愭偢

僷儚乕梡MOS-FET傪 0.1A掱搙偺僪儗僀儞揹棳偱VGS偺應掕傪峴偄婰榐偟偰偍偒傑偡丅

幚嵺偺傾僀僪儕儞僌揹棳偵嬤偄抣偺傕偭偲戝偒側揹棳偱應掕偟偨偄偲偙傠偱偡偑丄僪儗僀儞懝幐偵傛傞敪擬偱壏搙偺娗棟偑昁梫偲側傞偨傔偵丄應掕傪娙棯壔偟偰偄傑偡丅

0.1A偱傕壏搙曄壔偡傞偺偱丄庤憗偔應掕傪嵪傑偡昁梫偑偁傝傑偡丅

應掕抣偵嵞尰惈傪帩偨偣傞偨傔偵偼丄應掕帪偺婥壏偲埨掕壔揹尮偺揹埑側偳偺應掕忦審傕婰榐偟偰偍偒傑偡丅

師偵僶僀傾僗梡偺MOS-FET傪2mA掱搙偺僪儗僀儞揹棳偱VGS偺應掕傪峴偄丄

僷儚乕梡MOS-FET偺VGS偵嬤偄傕偺傪慖暿偟傑偡丅

僷儚乕梡MOS-FET偲慻傒崌傢偣偰丄僶僀傾僗梡偺MOS-FET偺僪儗僀儞揹棳偑5mA掱搙偺帪偵丄

僷儚乕梡MOS-FET偺僪儗僀儞揹棳偑0.3A掱搙偵側傞傕偺傪儁傾偵偟傑偡丅

嵟屻偵Nch偲Pch傪愙懕偟偰Vss偺彫偝偄傕偺傪僐儞僾儕儊儞僞儕偱儁傾偲偟傑偡丅

埲忋偼偲偭偰傕嬉戲側慖暿曽朄偱丄儁傾偺庢傟傞妋棪偑彮側偔婱廳側A儔儞僋儁傾偲側傝傑偡丅

偟偐偟偙偙偵徯夘偡傞傾儞僾偵偼丄偦傟傎偳偺尩偟偄慖暿偱側偔偰傕戝忎晇偱偡丅

壓恾偺夞楬偱丄Q1,Q2偺僪儗僀儞偵3mA乣5倣A掱搙傪棳偟偨帪偵丄Q5,Q6偺僪儗僀儞揹棳偑Q1,Q2偺僪儗僀儞揹棳偺50乣100攞偵側傟偽廩暘偵巊偊傑偡丅

偙偺帪偵Q1,Q2偺僜乕僗偲Q5,Q6偺僜乕僗娫偵揹埑嵎偑偁偭偰傕峔偄傑偣傫偐傜丄慻傒崌傢偣妋棪偑偩偄傇崅偔側傝傑偡丅偙傟偼A儔儞僋儁傾偲摨條偵巊偊傑偡偑丄儁傾偲偟偰偼奿棊偪偺B儔儞僋儁傾

偱偡丅

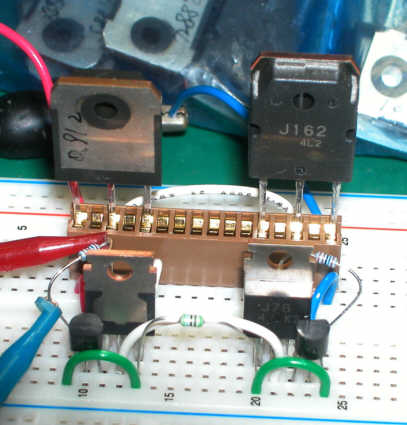

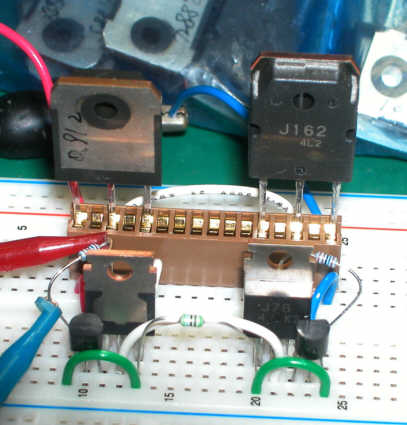

忋恾偺夞楬傪僽儗僢僪儃乕僪偵慻傒棫偰偰丄MOS-FET偺慖暿傪峴偄傑偟偨丅

偟偐偟偟偐偟偙傟偱慻傒崌傢偣偑偱偒側偔偰傕戝忎晇丅僎乕僩懁偵暘埑掞峈傪擖傟偰丄Q5,Q6偺偺僪儗僀儞揹棳傪揔摉偵崌傢偣傟偽巊偊傑偡丅偙傟

偩偲栿偁傝偺C儔儞僋儁傾偵側傝傑偡丅

偲塢偆偙偲偱懡暘偁傜備傞MOS-FET傪丄擟堄偺傾僀僪儕儞僌揹棳偵愝掕偱偒傞壜擻惈偑偁傝丄弌椡抜偺MOS-FET偼摉柺戝忎晇偲妝娤揑側尒捠偟偑偱偒傑偟偨丅

偟偐偟丄偙傟傑偱惉岟偟偨慻傒崌傢偣偺傛偆偵傾僀僪儕儞僌揹棳偑埨掕偟偰偔傟傞偺偐偼丄帋偟偰傒側偄偙偲偵偼暘傝傑偣傫偗偳偹丅

傾儞僾夞楬

2SK3954丆2SK2013丆2SJ618丆2SJ313偺慻傒崌傢偣偱A儔儞僋儁傾偑2儁傾摼傜傟偨偺偱丄壓恾偺夞楬偱嵟戝弌椡50W偺傾儞僾傪幚尡偟傑偟偨丅

RL=8兌丂f=1kHz丂Po=侾W 丂THD=0.0006亾

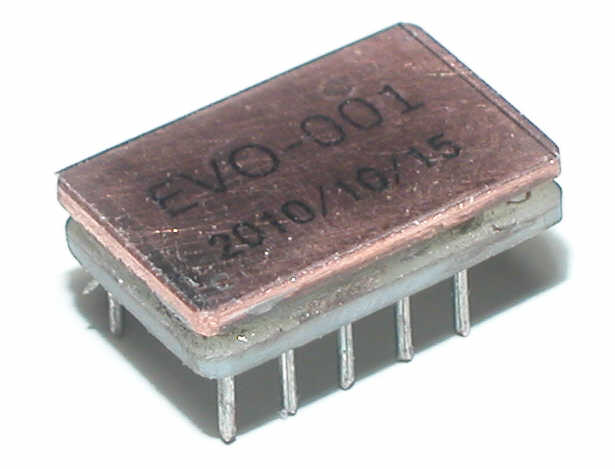

僴僀僽儕僢僪IC

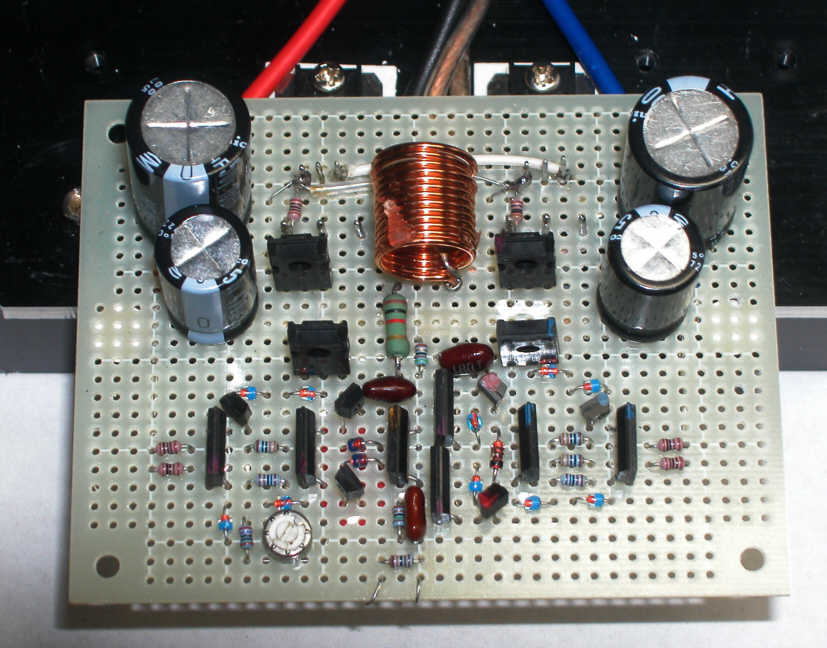

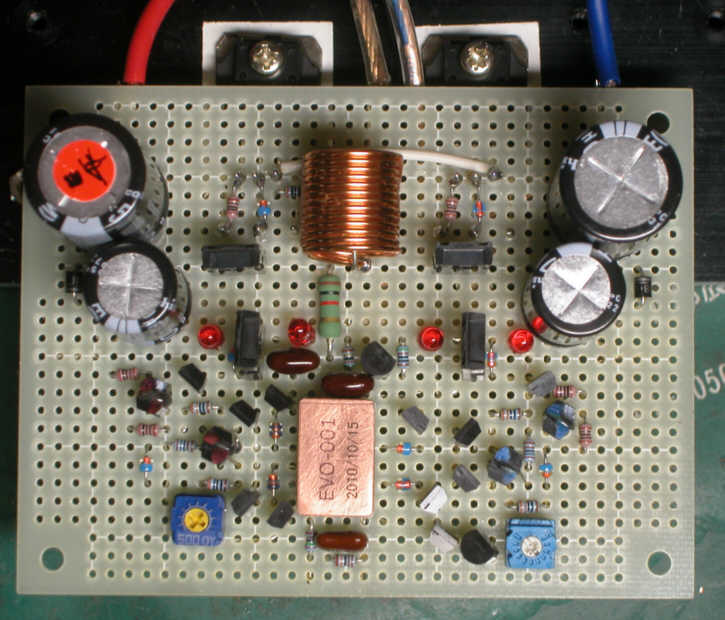

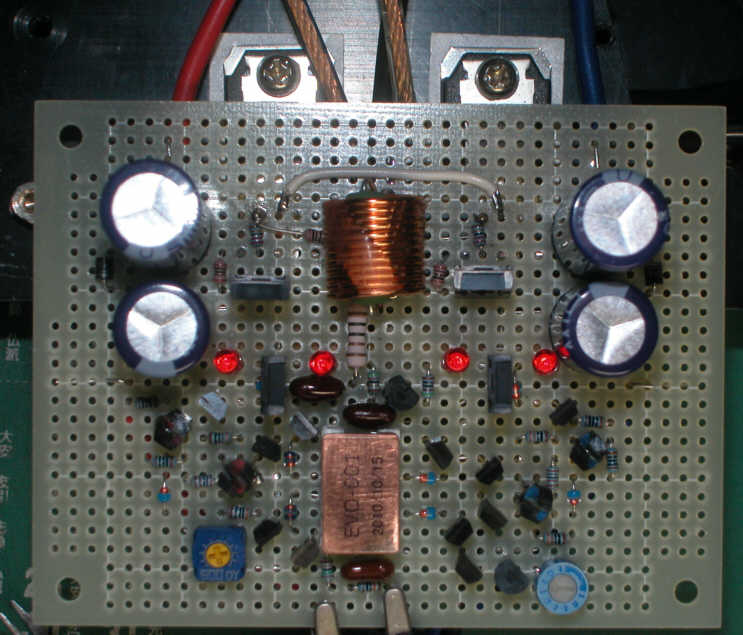

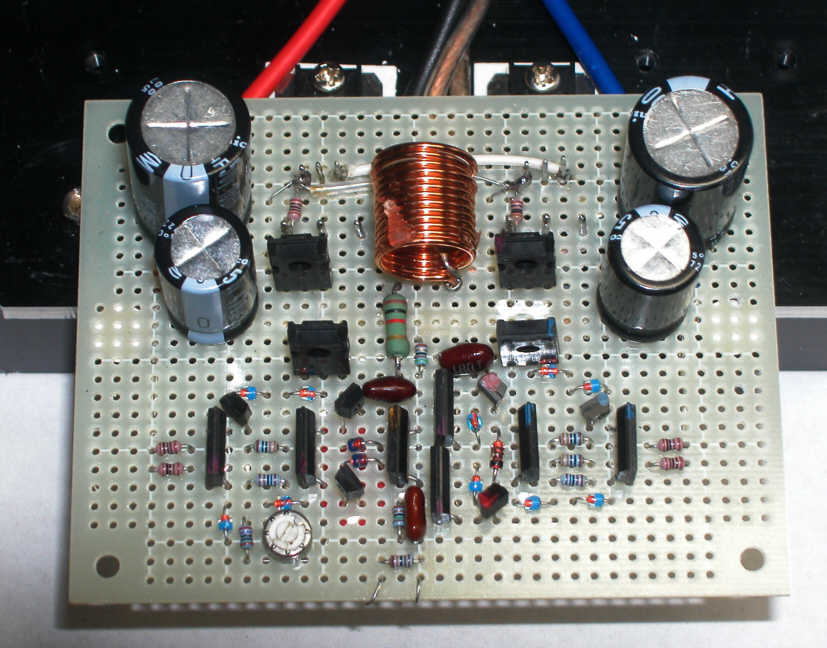

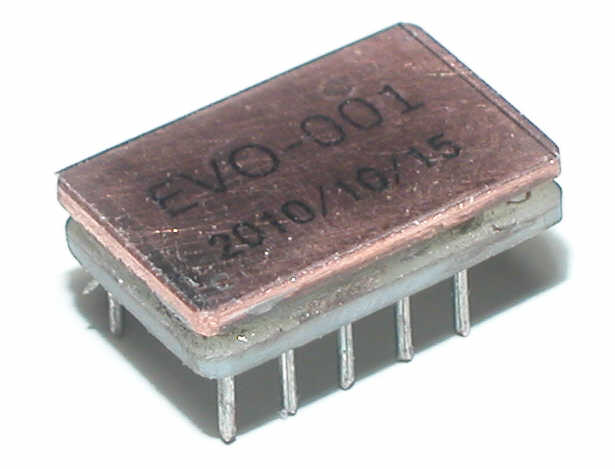

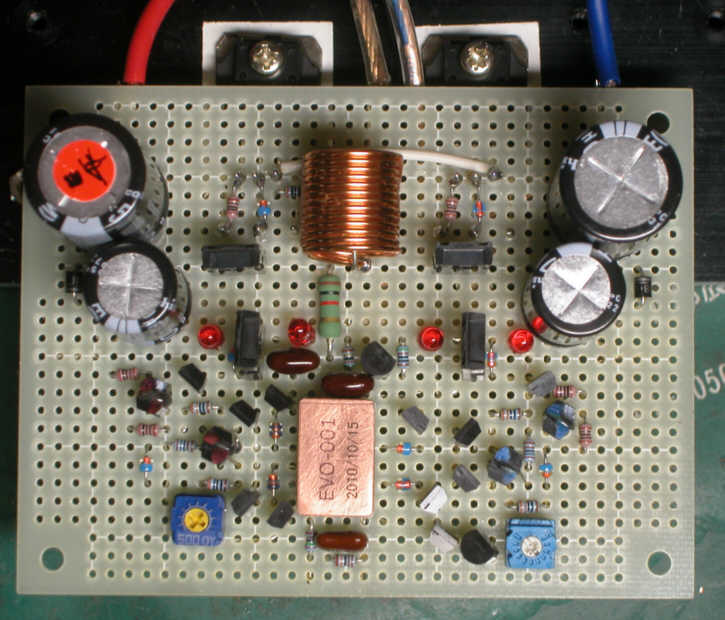

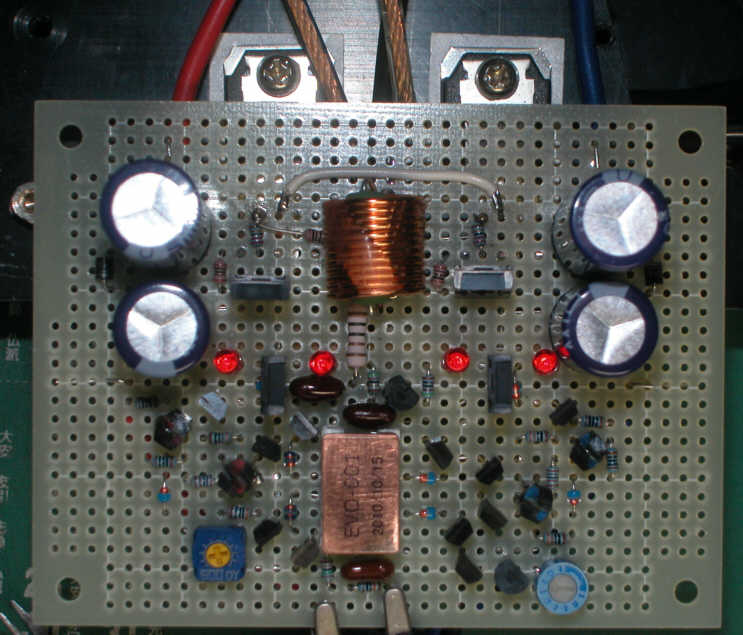

僨儏傾儖僞僀僾偺僨僶僀僗偑惗嶻懪愗傝偱擖庤崲擄偵側偭偰偄傞偨傔丄斈梡偺僠僢僾晹昳傪巊梡偟偰丄弶抜偺僋儘僗僔儍儞僩擖椡晹暘傪僴僀僽儕僢僪IC壔偟傑偟偨丅

摵斅傪忋晹偵挘傝晅偗偰惷揹僔乕儖僪偡傞偲摨帪偵丄僠僢僾娫偺壏搙嵎傪側偔偡傛偆偵偟偰偄傑偡丅

擬寢崌傪梫偡傞僇儗儞僩儈儔乕夞楬晹暘傕丄僨傿僗僋儕乕僩晹昳偱儌僕儏乕儖壔偟傑偟偨丅

儌僕儏乕儖撪晹偱嬻拞攝慄偟偰丄儕乕僪慄偺杮悢傪尭傜偟偰偁傝傑偡丅

揹尮揹埑偺曄摦偱弌椡僆僼僙僢僩揹埑偑曄壔偟傗偡偄偨傔丄掕揹棳夞楬傪僇僗僐乕僪壔偟偰懳張偟傑偟偨丅

帋偟偵嶌偭偨丄2SK1056丆2SK213丆2SJ160丆2SJ78偵傛傞C儔儞僋儁傾傪巊偭偨傾儞僾16W僷儚乕傾儞僾夞楬丅

偙偺夞楬偱2SK1056丆2SJ160偺僪儗僀儞丒僜乕僗娫揹埑傪30V埲忋偵偡傞偲丄敪怳偑妋擣偝傟偨偙偲傪晅偗壛偊偰偍偒傑偡丅

RL=8兌丂f=1kHz丂Po=侾W 丂THD=0.0009亾

丂

曻擬婍壏搙[T]懳傾僀僪儕儞僌揹棳[IQ]摿惈

曻擬婍偺壏搙偑忋徃偡傞偲傾僀僪儕儞僌揹棳偑尭彮曽岦偵曄壔偟傑偡偑丄壏搙忋徃偵傛傞傾僀僪儕儞僌揹棳偺曄壔偼彮側偔丄傾僀僪儕儞僌揹棳偺擬朶憱偼怱攝側偝偦偆偱偡丅

偟偐偟丄壏搙忋徃偟偰傕僪儗僀儞懝幐偺尭彮偑彫偝偄偨傔偵敪擬検偺尭彮偑彮側偔丄曻擬婍偺曻擬惈擻偑埆偄偲MOS-FET偺壏搙偑忋徃偟懕偗傞壜擻惈偑偁傝丄梋桾偺偁傞曻擬愝寁傗夁擬杊巭憰抲偺旛偊偑昁梫

偲峫偊傑偡丅

偄傛偄傛惢嶌偡傞偧両

傾儞僾夞楬偵丄揹尮夞楬丄弌椡DC揹埑専弌夞楬丄弌椡儈儏乕僥傿儞僌夞楬丄儔僢僔儏僇儗儞僩杊巭夞楬傪壛偊偨丄慡夞楬恾傪帵偟傑偡丅

僔僌僫儖僌儔僂儞僪SG偲僼儗乕儉僌儔僂儞僪FG偺娫偵僟僀僆乕僪偺弴曽岦揹埑暘偺僶儕傾傪擖傟偰丄僲僀僘儗儀儖偱偺僌儔僂儞僪儖乕僾傪抐偪愗傝丄擖椡攝慄僐乕僪偑僲僀僘

傪廍偆偲塢偭偨偙偲偺側偄傛偆偵抳偟偰偁傝傑偡丅

揹埑憹暆抜偺揹尮揹埑偑12V 埲壓偱偼摦嶌晄掕偱弌椡偵DC揹埑偑敪惗偡傞偨傔丄弌椡DC揹埑専弌夞楬偵怣崋偑擖傜側偄傛偆偵偟偰偄傑偡丅

弌椡抜偺揹尮揹埑偑捈楍愙懕偝傟偨僼僅僩僇僾儔LED偲僀儞僕働乕僞LED偺弴曽岦揹埑偺崌寁乮栺20V乯傪挻偊偰偐傜丄儔僢僔儏僇儗儞僩杊巭夞楬偲儈儏乕僥傿儞僌夞楬偑愝掕僞僀儈儞僌宱夁屻偵夝彍偟傑偡丅

弌椡偵栺0.6V埲忋DC揹埑偑敪惗偡傞偲丄弌椡DC揹埑専弌夞楬偵傛偭偰弌椡儈儏乕僥傿儞僌夞楬偺僼僅僩僇僾儔LED傪抁棈偡傞偺偱丄儈儏乕僥傿儞僌摦嶌偟偰弌椡抂巕偲傾儞僾傪愗傝棧偟丄僗僺乕僇偵DC揹埑偑妡偐傜側偄傛偆偵曐岇偟傑偡丅

弌椡DC揹埑専弌夞楬偑曐岇摦嶌偡傞偲丄揹尮傪愗偭偰弌椡DC揹埑専弌夞楬偺揹尮揹埑偑0V嬤偔傑偱壓偘側偄偲夝彍偟傑偣傫丅

惓晧揹尮傪慡偰撈棫偺僽儕僢僕惍棳夞楬曽幃偲偟偰丄傾乕僗儔僀儞偵惍棳夞楬偺儕僢僾儖揹棳偑崿擖偟側偄傛偆偵攝慄偟傑偟偨丅

巊梡偟偨婎斅偼僒儞僴儎僩偺彫宆儐僯僶乕僒儖婎斅丂ICB-293G偱偡丅

椺偵傛偭偰摵敁僷僞乕儞傪僄僢僠儞僌塼偱彍嫀偟偰丄扨側傞寠偁偒僈儔僗僄億僉僔婎斅偲偟偰偄傑偡丅

攝慄偺岎嵎偡傞晹暘偑帄傞強偵偁傞嫢埆偺攝慄僷僞乕儞偱偟偰丄棫懱岎嵎揰偱偼僥僼儘儞僠儏乕僽傗僥僼儘儞僥乕僾偱愨墢偟偰儈儖僼傿乕儐忬懺偵側偭偰偄傑偡丅

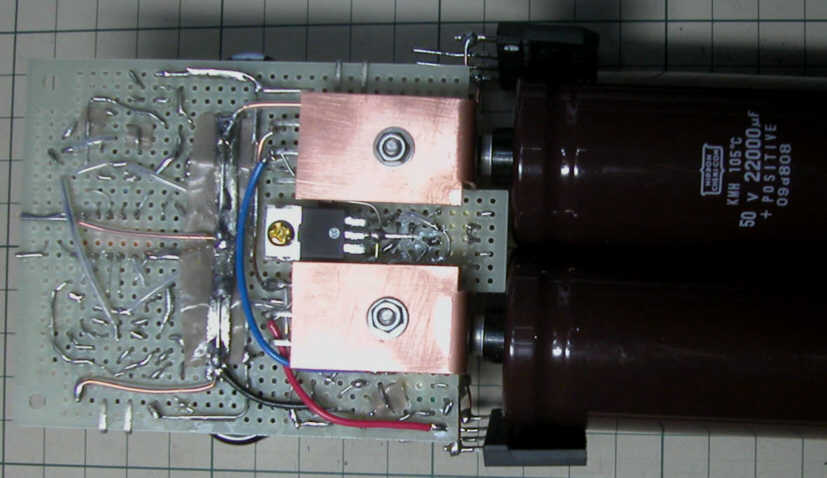

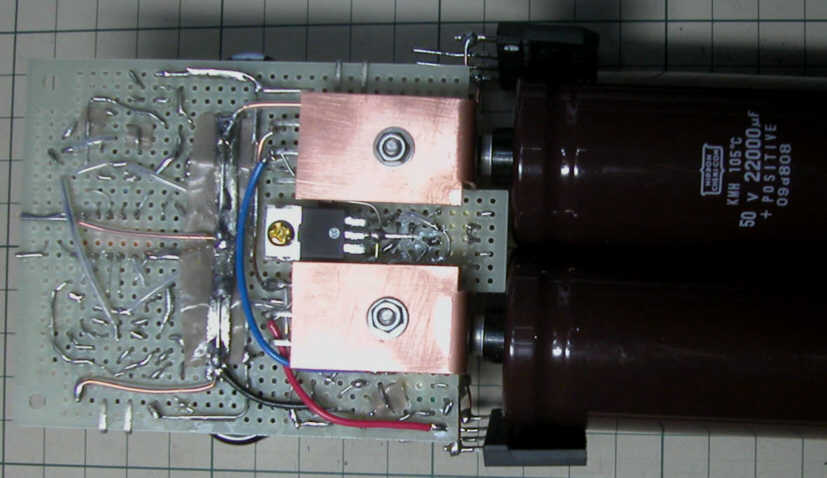

弌椡抂巕傊偺攝慄OFC働乕僽儖偼丄MOS-FET偺僪儗僀儞偱偁傞僼儔儞僕偺寠偵丄埑拝抂巕傪巊偭偰價僗丒僫僢僩偱愙懕偟偰偄傑偡丅

弌椡抜MOS-FET偺僪儗僀儞偲僽儘僢僋僐儞僨儞僒偺揹嬌傪偮側偖1mm岤摵斅偵傛傞揹嬌斅

峸擖偟偨1mm岤摵斅偼僔儍乕儕儞僌愗抐偟偰偁傞偨傔丄愗抐晹暘偺暯柺惈偑埆偔丄1cm埵傪愗傝幪偰偰巊偆丅

壛岺屻偵嵶栚偺桘搖愇偱杹偄偰僶儕傗僄僢僕傪庢傝彍偔丅

MOS-FET庢晅僱僕偺捠傞寠偵偼丄愨墢偺偨傔偵撪宎3mm偺僥僼儘儞僠儏乕僽傪1mm埲撪偺暆偱椫愗傝偵偟偨傕偺傪擖傟傞丅

偆偭偐傝擖傟朰傟偨傝丄寠偐傜奜傟偰偟傑傢側偄傛偆偵丄慻傒棫偰傞嵺偼拲堄偟丄僥僗僞乕偱僱僕偲揹嬌斅娫偺愨墢僠僃僢僋傪偡傞丅

夞楬枅偺攝慄偺廔椆帪揰偱拞娫摦嶌僥僗僩傪幚巤偡傞丅

|

嵍恾偵

揹埑憹暆抜夞楬偺僥僗僩梡偺壖攝慄傪惵怓偱帵偡丅

揹尮僶僀僷僗僐儞僨儞僒傪嵟抁愙懕偟側偄偲崅堟敪怳偟偰挷惍晄擻偵側傞丅

2SA1360偺僐儗僋僞揹埑傪僆僔儘僗僐乕僾偱尒偰VR50兌偱0V偵崌傢偣傞丅

Rc100兌偺抂巕揹埑傪500mV掱搙偵RT傪壖挷惍偡傞丅愒暥帤偺揹棳偼愝寁忋偺偍傛偦偺憐掕抣偱栚昗抣偱傕幚應抣偱傕側偔丄扨側傞嶲峫偺偨傔偱偡丅 |

丂

|

嵍恾偵

弌椡DC揹埑専弌夞楬偺僥僗僩梡偺壖攝慄傪惵怓偱帵偡丅

弌椡DC揹埑偺戙梡偵1.5V偼姡揹抮偱丄嬌惈傪媡偵偟偰傕摦嶌偡傞偙偲傪妋擣偡傞丅

摦嶌偡傞偲TLR123偑揰摂偡傞偲摨帪偵TLP222A偺僗僀僢僠偑ON偡傞偺偱丄僥僗僞乕偱摫捠僠僃僢僋偡傞丅

揹尮傪愗傞傑偱TLP222A偺僗僀僢僠偑ON偟懕偗傞丅

TLR123偼揰摂偟偰曐岇摦嶌偺昞帵傪偡傞偩偗偱偼側偔丄偦偺弴曽岦揹埑傪曐岇摦嶌傪曐帩偡傞偨傔偵巊偭偰偄傞丅 |

丂

|

嵍恾偵

弌椡DC儈儏乕僥傿儞僌夞楬偺僥僗僩梡偺壖攝慄傪惵怓偱帵偡丅

僼僅僩僇僾儔偵10mA掱搙偺揹棳傪棳偡偲丄2昩掱偺僞僀儈儞僌偱儘乕僪僗僀僢僠偺MOS-FET偑ON偡傞偐傜丄僥僗僞乕偱摫捠僠僃僢僋偡傞丅

儘乕僪僗僀僢僠偵巊梡偟偨IRFB3077偼丄TO-220僷僢働乕僕偱偁傝側偑傜僆儞掞峈偑2.8m兌偲掅偔2偮捈楍偱6m兌掱搙偩丄偙偺僆儞掞峈偼I倓偺旕朞榓椞堟偺摿惈偱捈慄惈偑崅偄丅

崿摨偟偰偄傞偐傕抦傟側偄偺偱堦尵丄C-MOS傾僫儘僌僗僀僢僠偲偄偆偺偼怣崋揹埑偱僎乕僩丒僜乕僗娫揹埑偑曄壔偟偰僆儞掞峈偑曄壔偡傞偑丄偙偺儘乕僪僗僀僢僠偼廩暘偵崅偄堦掕偺僎乕僩揹埑偱僆儞偡傞偨傔偵丄偦傟偲偼尨棟揑偵堎側傞丅 |

丂

|

嵍恾偵

儔僢僔儏僇儗儞僩杊巭夞楬偺僥僗僩梡偺壖攝慄傪惵怓偱帵偡丅

僼僅僩僇僾儔偵10mA掱搙偺揹棳傪棳偡偲丄1昩埲撪偺僞僀儈儞僌偱儘乕僪僗僀僢僠偺MOS-FET偑ON偡傞偐傜丄僥僗僞乕偱摫捠僠僃僢僋偡傞丅

儔僢僔儏僇儗儞僩杊巭夞楬偺僽儕僢僕僟僀僆乕僪偼丄揹尮AC揹埑偵娷傑傟傞DC惉暘傪梷惂偟偰揹尮僩儔儞僗偺歑傝傪尭傜偡栶栚傪寭偹偰偄傞丅

丂 |

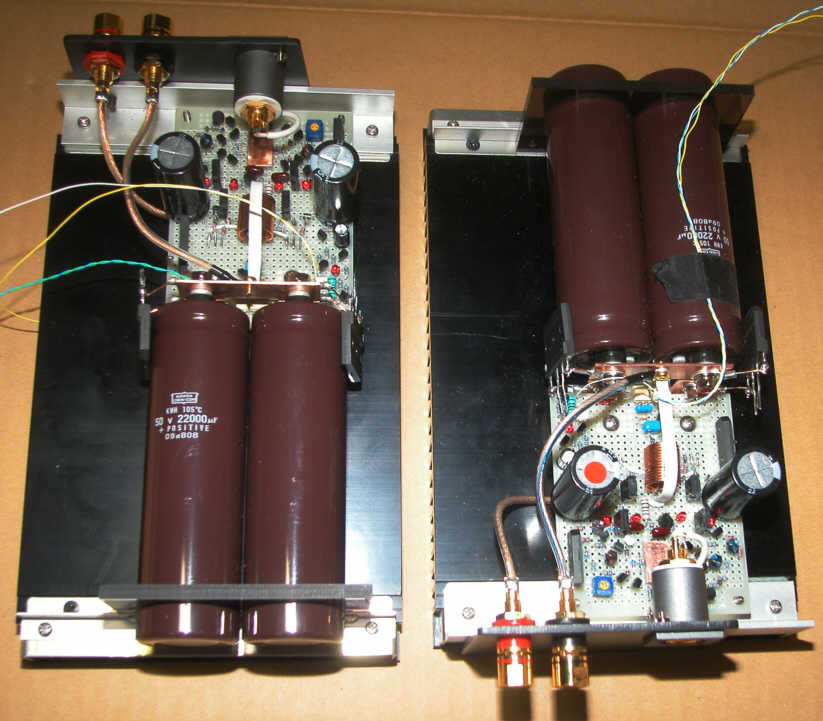

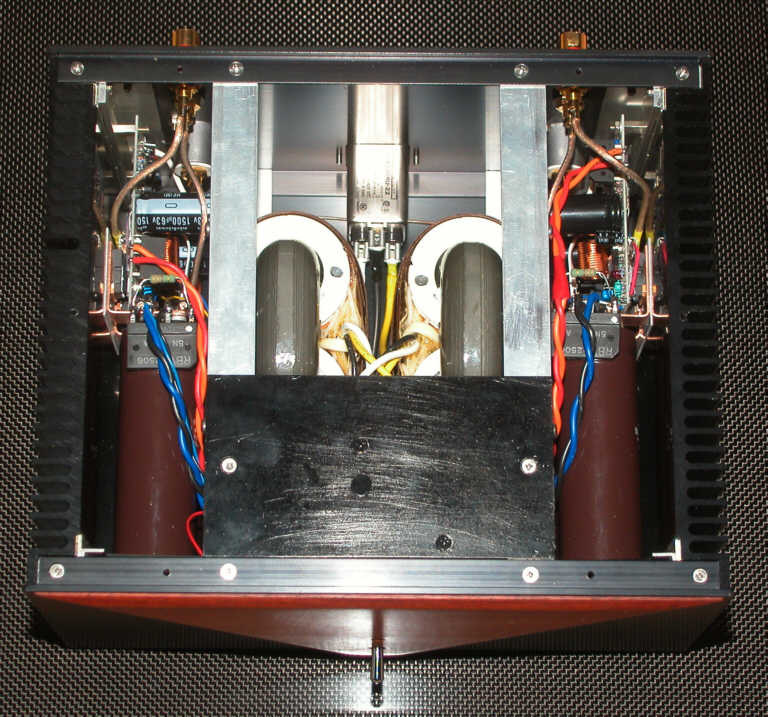

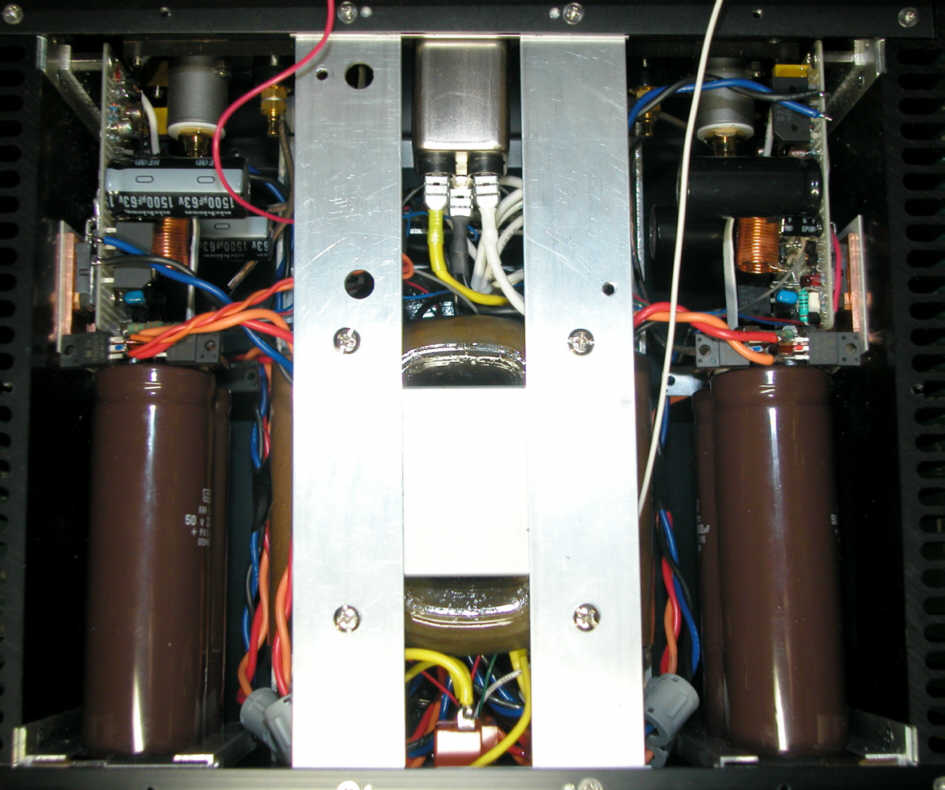

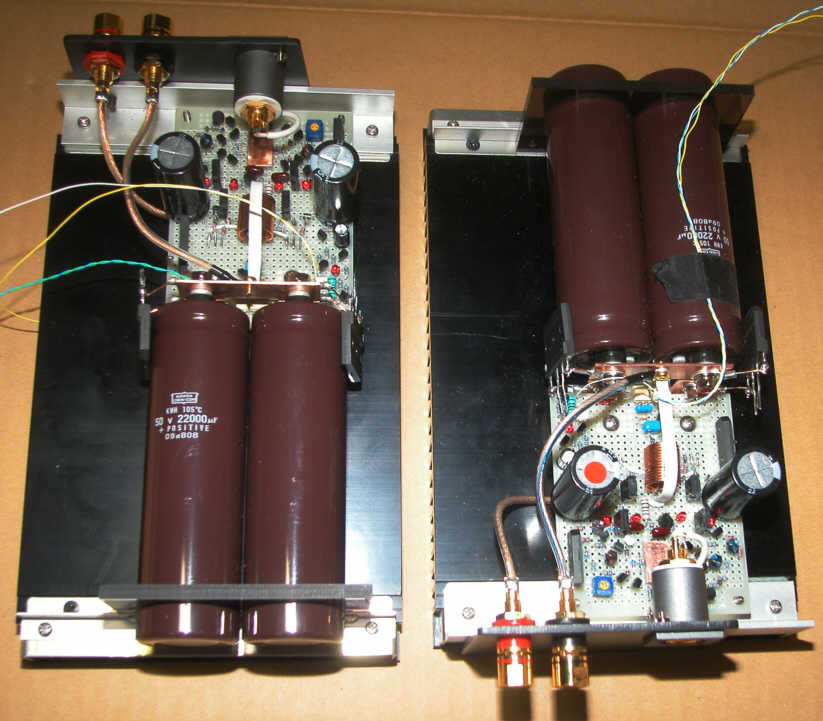

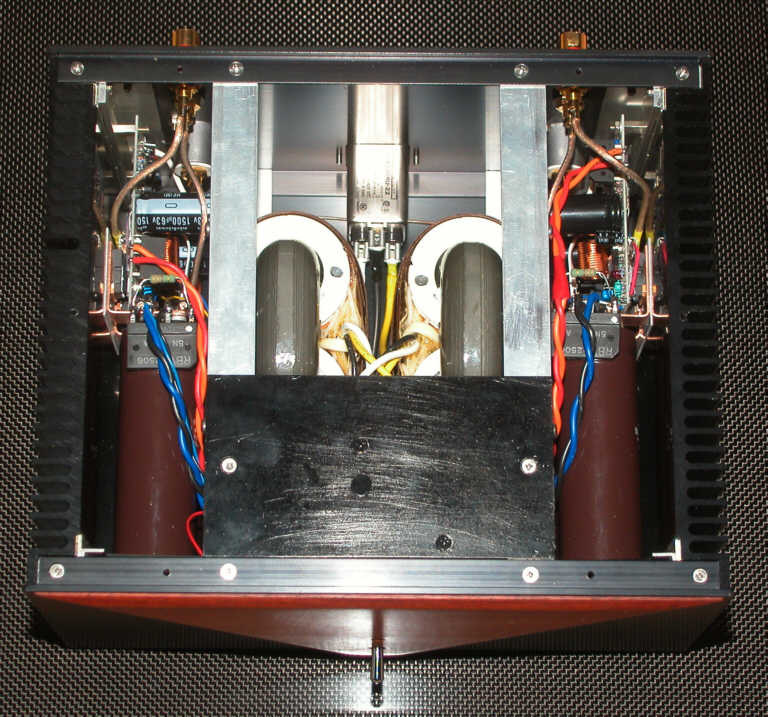

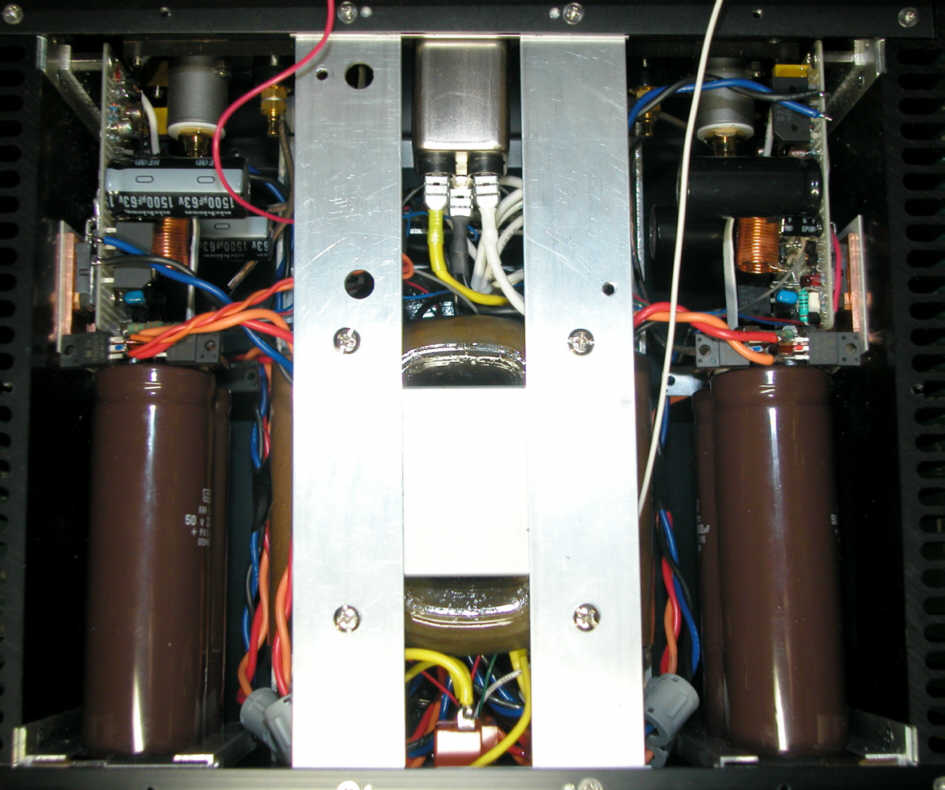

傾儞僾夞楬偲擖弌椡抂巕偲曻擬婍偲揹尮惍棳夞楬傪堦懱偺儐僯僢僩偵偟偰丄偙傟偵揹尮僩儔儞僗偐傜偺揔摉側AC揹埑傪偮側偖偩偗偱嵪傓傛偆偵偟傑偟偨丅

弌椡抜MOS-FET偺僪儗僀儞偲僽儘僢僋僐儞僨儞僒偺揹嬌傪摵斅偱嵟抁愙懕偟偰偄傑偡丅

働乕僗偵慻傒崬傓慜偵亄亅30V DC揹尮傪弌椡抜MOS-FET偺僪儗僀儞偵愙懕偟偰丄傾僀僪儕儞僌揹棳偲弌椡DC僆僼僙僢僩揹埑偺挷惍傪偟傑偡丅

偙偺帪偵揹埑憹暆抜偺揹尮傪愙懕偟側偔偰傕丄僟僀僆乕僪傪夘偟偰弌椡抜懁偐傜嫙媼偝傟傑偡丅

揹尮揹埑偑曄傢偭偰傕傾僀僪儕儞僌揹棳偺曄壔偼彮側偄偺偱丄偙傟傪嵟廔挷惍偲偟傑偟偨丅

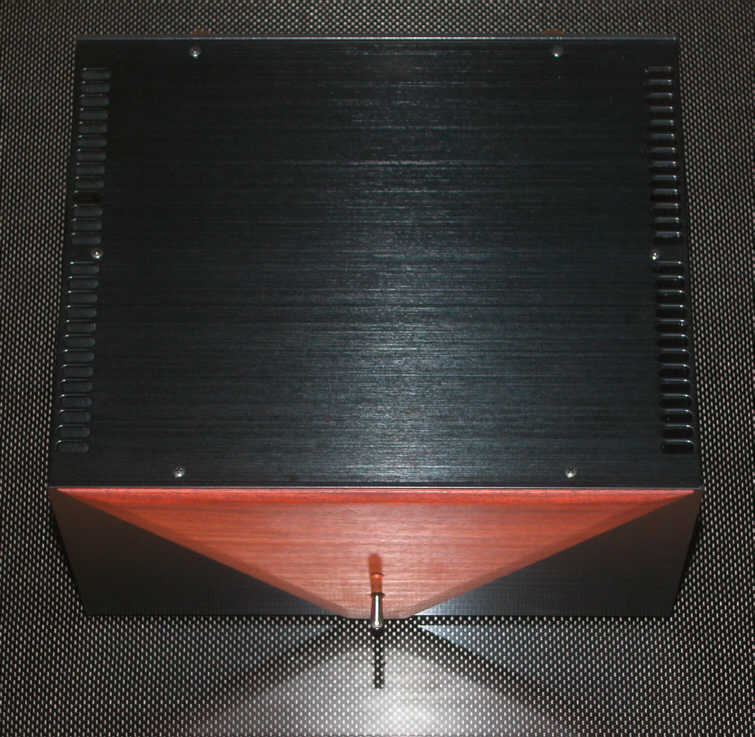

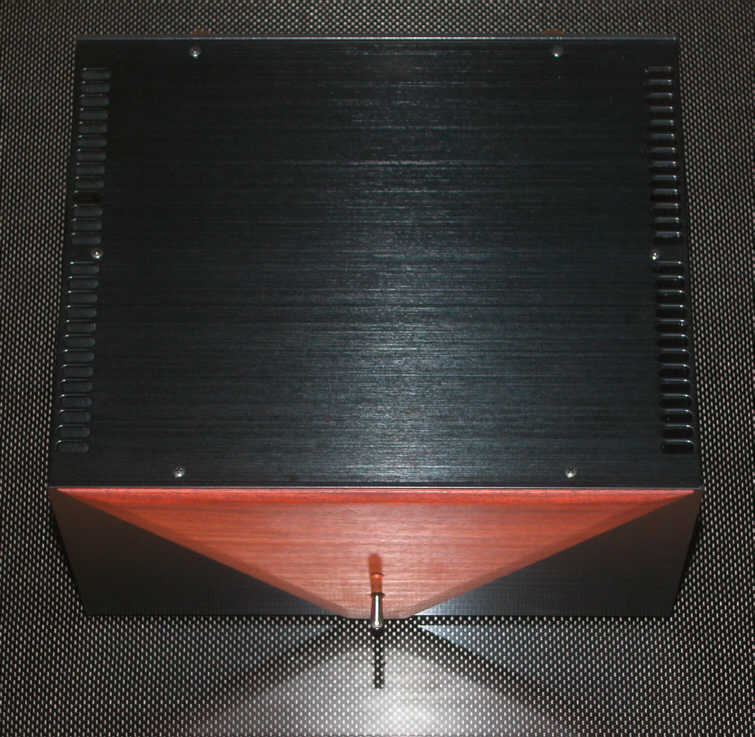

僸乕僩僔儞僋偲堦懱偺攚柺抂巕斅傪僗儉乕僘偵拝扙壜擻偲偡傞偨傔偵丄攚柺僷僱儖傪僥乕僷乕忬偵偊偖傝庢偭偰偁傝傑偡丅丂

僞僇僠働乕僗偺拞偱偼嵟戝僒僀僘偺僸乕僩僔儞僋傪帩偮HY149-29-23BB偵慻傒崬傒傑偟偨丅

僼儘儞僩僷僱儖偵偼廮傜偐偱塻偄昞忣傪弌偡偨傔偵丄壴棞偺5mm岤斅傪僔儍乕僾偵嶍偭偰挘傝晅偗傑偟偨丅

撪晹丄夦偟偄崟偄僇僶乕偺壓偵偼儔僢僔儏僇儗儞僩杊巭夞楬偺婎斅偑愽傓丅2偮偺R僐傾揹尮僩儔儞僗傪懳岦偝偣偰楻傟帴懇傪暵偠崬傔偰偄傞丅

僴儎僽僒偺僀僆儞僄儞僕儞偲偺堘偄傪尒偣偮偗傞丄4婡偲傕惓忢側摦嶌偺岝巕椡僀儞僔儏儗乕僞偺婸偒丅

僗僀僢僠傪偪偭偪傖偄僠儞僐偭偰丄偳偆偟偰傕僷儞僣偵尒偊偪傖偆偐丄儅傽偦傟偱傕偄偄傗丅

杮懱廳検丗丂10.5kg

奜宍悺朄乮mm乯丗丂W 280亊H 156 (働乕僗149+媟晹7乯亊D 268

(僗僀僢僠晹15+僷僱儖崬傒杮懱235+僞乕儈僫儖晹18)

惢憿尨壙丗 栺亸500,000丂乮嵽椏旓亄楯捓亄媄弍椏etc.乯

廃攇悢摿惈丂(0dB=1W/侾倠Hz/8兌) 丂 -3dB億僀儞僩偼360kHz

弌椡揹椡懳榗棪摿惈恾丂乮廃攇悢1kHz丂晧壸8兌乯

廃攇悢懳榗棪摿惈恾丂乮弌椡1W丂晧壸8兌乯

嵟戝弌椡丗丂48W+48W 乮RL=8兌乯丂丂80W+80W (RL=4兌乯

弌椡僀儞僺乕僟儞僗丗丂0.03兌 (f=1kHz乯

巆棷僲僀僘丗丂110兪V 乮僲乕僂僄僀僩乯丂丂丂丂18兪V 乮JIS-A 僼傿儖僞乯

徚旓揹椡儚僢僩僠僃僢僇乕偱應掕丗丂柍擖椡帪 47W

8兌椉僠儍儞僱儖嵟戝弌椡帪 185W

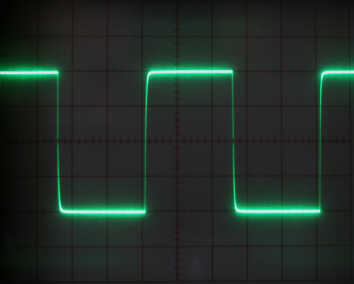

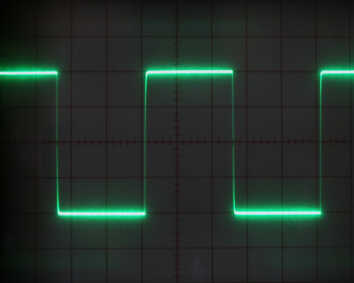

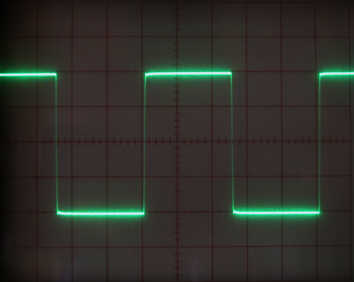

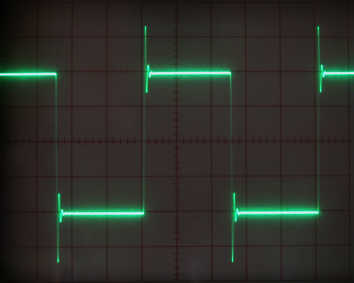

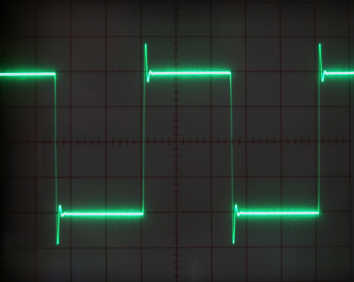

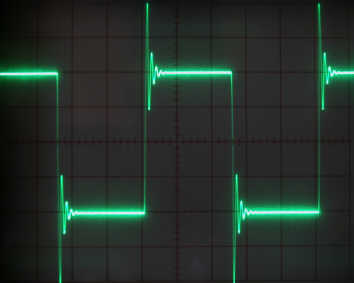

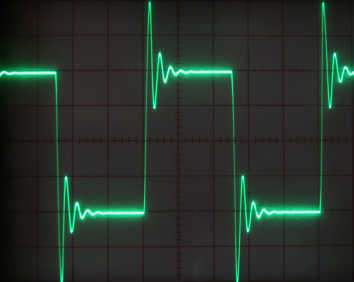

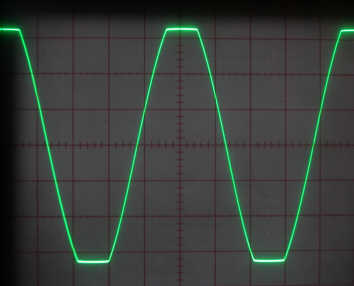

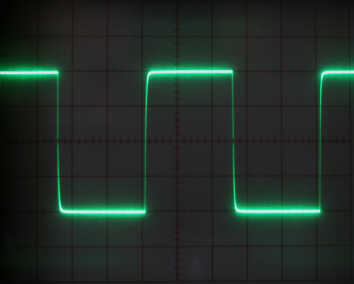

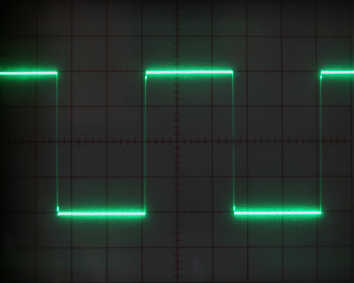

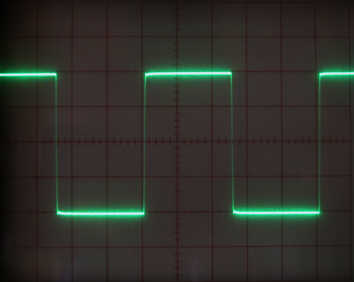

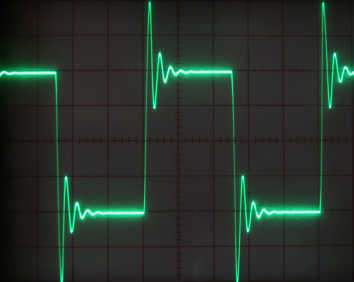

10kH倸曽宍攇弌椡攇宍丂悅捈幉 1V/div

8兌掞峈晧壸偺傒

|

柍晧壸忬懺

|

8兌偲0.01兪F偺暲楍晧壸

|

0.01兪F偺梕検晧壸偺傒

|

8兌偲0.047兪F偺暲楍晧壸

|

0.047兪F偺梕検晧壸偺傒

|

8兌偲0.1兪F偺暲楍晧壸

|

0.1兪F偺梕検晧壸偺傒

|

8兌偲0.47兪F偺暲楍晧壸

|

0.47兪F偺梕検晧壸偺傒

|

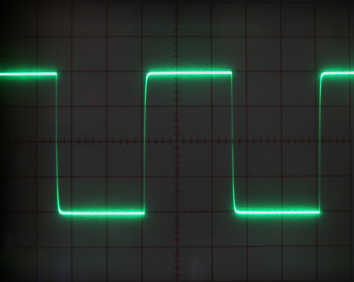

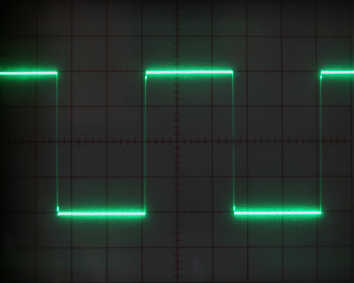

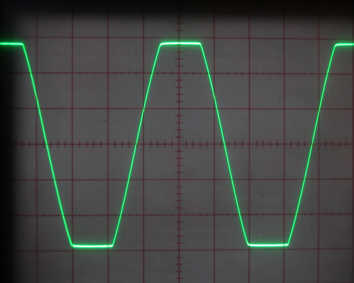

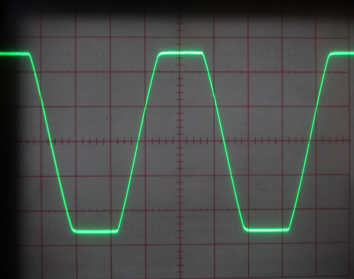

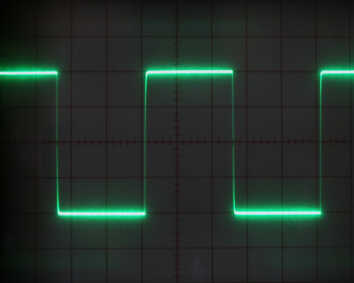

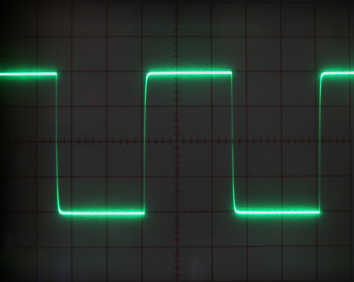

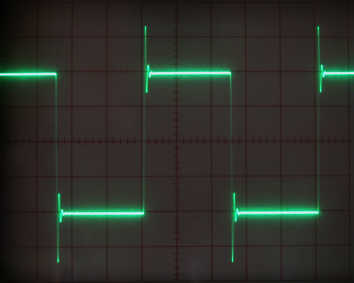

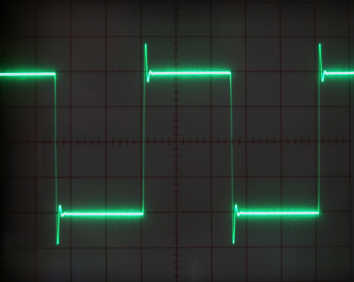

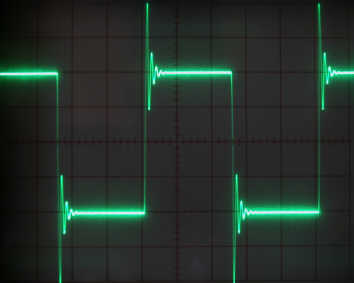

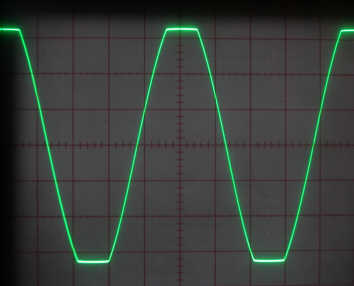

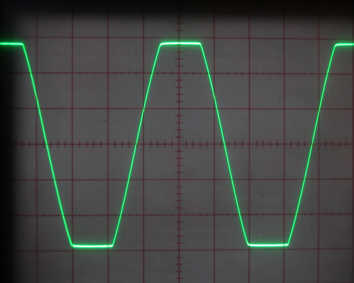

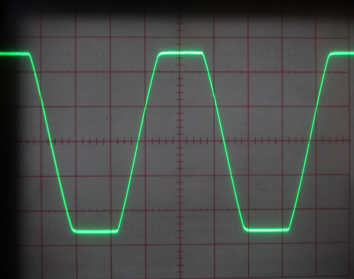

10kHz僋儕僢僾攇宍丂悅捈幉 10V/div

柍晧壸

|

8兌晧壸

|

4兌晧壸

|

傾僺乕儖億僀儞僩

偙偺傾儞僾偺揹埑憹暆抜悢偼偨偭偨偺1抜偱偡丅

偦偺揹埑僎僀儞傪惗傒弌偟偰偄傞偺偼嬐偐悢mS偺J-FET偲旕椡偱偡丅

偦偺彫偝側憹暆椡傪儘僗偣偢惓妋偵揱払偡傞偙偲偵搘椡傪惿偟傑偢夞楬僥僋僯僢僋傪嬱巊偟丄昁梫側晹昳傪傆傫偩傫偵搳擖偟偰偄傑偡丅

MOS-FET偵傛傞弌椡抜傕丄僜乕僗掞峈傪庢傝彍偄偰MOS-FET偺gm傪懝偹側偄夞楬偵偟偰偁傞偨傔丄懡悢僷儔愙懕偲偟側偔偰傕僔儞僌儖偱偁傝側偑傜丄廩暘偵掅偄弌椡僀儞僺乕僟儞僗傪幚尰偟偰偄傑偡丅

斀徣揰

儌僲儕僔僢僋僨儏傾儖慺巕傪巊傢側偐偭偨偨傔偵DC僪儕僼僩偑弌傑偡偑丄傾儞僾偲偟偰偼幚梡忋偺栤戣偼偁傝傑偣傫丅DC100亾NFB偲偐丄DC僒乕儃偲偐懳嶔偼偁傝傑偡

偑丄偦偺曽朄偼巹偺庯枴偵岦偐側偄偺偱徚嬌巔惃偱偡丅

夁揹棳儕儈僢僞乕傪愝偗偨偐偭偨偗傟偳丄曐岇夞楬偺偨傔偵揹尮僩儔儞僗傪暿偵偡傞偲偐柺搢偵側傞偺偱傗傔傑偟偨丅

僼儘儞僩僷僱儖傪偙偙偵偁傞傛偆側昞忣偺偁傞栘栚偵偟偨偐偭偨偗傟偳丄

揔摉側斅嵽偑尒偮偐傜偢巆擮丅

摉弶偺尋媶栚揑偼幚尡抜奒偱払惉偱偒偰偄偨偐傜丄偙偙傑偱姰惉偝偣偰偟傑偆昁梫側偳側偐偭偨偺偵丄傑偨埆偄暼偑弌偰偟傑偭偨丅

|

2SK3497/2SJ618

Power Amplifier

擉戙栚 |

|

僴僀僽儕僢僪IC傪梋暘偵嶌傝夁偓偨偺偱丄偦傟傪徚壔偡傞偨傔偵惈挦傝傕側偔摨偠傾儞僾傪惢嶌偟傑偟偨丅

LED偺寠偵僉儏乕價僢僋僕儖僐僯傾傪浧傔崬傫偱偍煭棊偟傑偟偨偑丄慡斀幩偡傞僇僢僩偺巇曽偱偁傞偨傔偵岝偺摟夁偑彮側偄偲偄偆擄揰偑偁傝傑偡丅

巹偺惈暘偐傜偟偰傑偭偨偔摨偠傕偺傪憿傞偙偲偑柍棟側傫偱丄偦傟偱壗偐怴偟偄帋傒偵挧愴偟傛偆偲埆懌憕偒傪偟偰傒偨偗傟偳丄寢嬊丄尦偺忊偵栠偭偨傛偆側宱堒偲側傝傑偟偨丅

僼儘儞僩僷僱儖偵擮婅偩偭偨昞忣偺偁傞栛栚偺斅傪庢傝晅偗偰偼傒偨偑丄壗偩偐側乣丄巹偺婜懸抣傪壓夞偭偰偄傞偟丄憿傜側偄曽偑椙偐偭偨偐傕丅

偙偺傾儞僾傪傕偭偰惉弉搙側傝姰惉搙偑1抜奒忋偑偭偨偙偲偼帠幚偩偐傜椙偟偲偟偰偍偔傋偒偐丅

庡側曄峏揰偼丄揹埑憹暆抜偺掕揹棳夞楬偺僇僗僐乕僪夞楬偺僶僀傾僗揹尮偵惵怓LED傪巊偄丄掕揹棳夞楬偺僩儔儞僕僗僞偺Vce傪彮偟崅偔偟傑偟偨丅

MOS-FET儘乕僪僗僀僢僠夞楬傪偙偺夞楬傪嶲峫偵丄僼僅僩僇僾儔傪堦屄嶍尭偟傑偟偨丅

偦偺 戙傢傝丄偙偙偵偼崅VEBO乮12V埲忋乯偺 僩儔儞僕僗僞傪昁梫

偲偟傑偡丅

弌椡抜偺揹尮惍棳偵僔儑僢僩僉僶儕儎僟僀僆乕僪傪梡偄傑偟偨丅

揹尮僩儔儞僗傪LR嫟捠偵偟偰丄弌椡抜偲揹埑憹暆抜偱暘偗傑偟偨丅

弌椡偺DC僪儕僼僩偑亇50倣V

埵偁傞偨傔丄徚嬌揑側懳嶔偱偡偑丄DC惉暘傪慡晧婣娨偡傞傛偆偵夵憿偟傑偟偨丅偙傟偱弌椡偺DC僪儕僼僩偼1/20偵尭彮偟傑偟偨丅

偦傟偲堷偒姺偊偵丄婣娨儖乕僾偵戝梕検偺僐儞僨儞僒傪擖傟偨偣偄偱丄揹尮傪愗偭偰嵞搳擖偡傞嵺偵2乣3暘抲偐側偄偲丄曐岇夞楬偑摥偄偰偟傑偆偲偄偆怴偨側栤戣偑偱偒傑偟偨丅

偙傟偱壒偑曄傢偭偨偐偼敾傝傑偣傫丅

堦戜栚偼僗僺乕僪姶偺偁傞僷儕僢偲偟偨壒偱偡偐丄2戜栚偼僔僢僩儕姶偲偄偆偐朿傛偐偱娵傒偑偁傝丄傾僀僪儕儞僌揹棳偺堘偄偑尨場偲巚偄傑偡丅

丂