INDEX

Evolve Power Amplifiers * Links

[ボルテージ・ミラー回路][本機の設計][本機の回路][本機の製作][本機の調整][ソース・フォロワ回路への変更][本機の特性]

ボルテージ・ミラー方式 、無帰還 、DC

2SJ113/2SK399 SEPP AB級40W ステレオ パワーアンプ

MJ無線と実験 1992年6月号 に発表

出力段のパワーMOS-FETに、ボルテージ・ミラーと名付けたシンプルで強力なマイナーループNFBを掛けて、オーバーオールのNFBを掛けることなく,極めて低い出力インピーダンスを実現した,ナチュラルな音のアンプです。

|

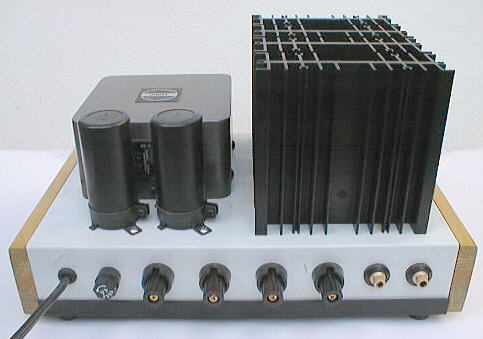

シャシーはリードS4(300×200×60)を使用。両サイドに手製のウッドパネルを配しました。 |

|

シャシー上に出ているブロックコンデンサーが電圧増幅段用の小型な方のため、電源トランスと放熱器が堂々と見えますが、実物はコンパクトで軽量です。 |

|

出力ターミナルと入力端子にはスーパートロンを奮発しました。 |

|

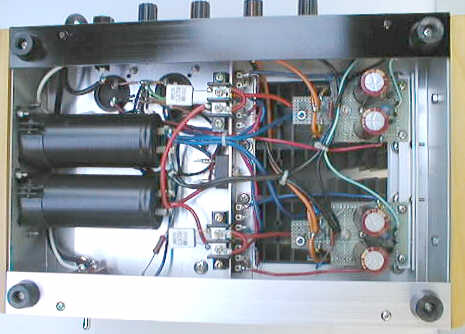

基板を放熱器の下に配して出力段パワーMOS-FETとの配線を短縮したため、ゲート直列抵抗を入れなくても発振しません。 |

|

配線を少し変えるだけで、ボルテージ・ミラー回路からソース・フォロワ回路に変更できます。 ボルテージ・ミラーの動作条件を満足する基本設計だから、ソース・フォロワに変更しても高いクオリティの音が得られるのです。 |

ボルテージ・ミラー回路とは,図1に示すように,MOS-FETのソース・フォロワ回路と向かい合わせに,ゼロバイアス動作のJ-FETを追加して,出力段に局部帰還を掛けた回路です.

|

|

J-FETのドレイン側は,ドライブ段TrのコレクターとMOS-FETのゲートであるため,高インピーダンスとなっています.

NchとPchのJ-FETドレイン同士は,インビーダンスの低いMOS-FETのバイアス電源VBで結合してあります.

そのため,ドライブ段からの信号電流ISは,J‐FETのソース抵抗RSに流れ,J‐FETのソース側に信号電圧VSが発生し,MOS‐FETのソース側にVSと等しい出力電圧VOが得られます.

J‐FETのドレイン側インピーダンスZDが高いほど,出力インピーダンスZOが小さくなりますが,MOS-FETの入力容量Cis(ゲート側から見たすべての容量,帰還容量も含まれる)のために,周波数が高くなるほどZDが低下し,ZOが増大します.

MOS-FETのゲート‐ソース間電圧VGSは,最大でもVB以上とならないことから,ドレイン電流IDの最大量が制限されるため,過大電流を防止する効果がありますが,最大出カが電流制限作用でクリップしてしまわないように設計しなければなりません.

そのためMOS-FETには,スレッショルド電圧VGS(th)と相互コンダクタンスgmの高いことが望まれます.

幸いにも,豊富なスイッチング用パワーMOS-FETの中には,その要求に合致したものが多くあります.

MOS‐FETには日立の2SJ113/2SK399を用いました.

伝達特性を図2に示します.

アイドリング電流IOを1Aとすると,図2からVGSは5V程度になりますから,VBはVGSのおよそ2倍の10Vとなります.

|

|

2SJ113/2SK399に掛かる最大のVGSは,前述の原理からVBの10V以内です.

VGSが9Vの場合のIDは約9Aですから,2Ωの負荷抵抗でも18Vの出力電圧が得られるので,低負荷インピーダンスにも十分耐えられます.

基本設計のための回路を図3に示します.

電源トランスに,タンゴのトロイダルトランスRS‐3101を用いたので,出力段の電源電圧VDDは約32Vです.

IOを大きく設定すればVBを高くできて,電流クリップ時のIDを大きくできますが,反面MOS-FETの発熱量が増大し,チャンネル損失PCHの許容量をオーバーしてしまうため,本機のIOは1Aとしました.

表1の規格表から PCH =100W (Ta=25℃) , TCH =150℃ であるため, 内部熱抵抗θi は デンカ放熱シートTO-3Pを使用したMOS-FETと放熱器の間の熱抵抗は, 下に示す図は熱伝導の回路です. |

|

| PCH =VDD・IC = 32V×1A=32W であるため, 放熱器に許される最高温度 Tf を求めると, Tf =TCH - PCH

(θi +θc +θs 放熱器周囲の気温Taが50℃の場合に, θf = (Tf -Ta)/PCH |

図4の放熱設計から,放熱器の温度を86℃以下に保たなければなりません.

そのため,放熱器にフレックスのTF1212(122x120×40)を4枚に,MOS-FETを1個ずつ取り付けて,シャシーの上に載せるオープンスタイルとしました.

バイアス回路は図5のように,VBよりも1~2V低い電圧のツェナーダイオードと,可変低抗器(VR)で調整できるようにしました.

[図5] バイアス回路

この回路はVRが接触不良を起こすと,IOが増加して危険なので,VRには信頼性の高いものを使用します.

このバイアス回路が定電圧動作する最小電流ILは約2mAです.

ボルテージ・ミラーの局部帰還回路に用いたJ-FETは2SJl08/2SK370のGRランクIDSS 5.5mAですが,同程度のgm と IDSSなら,他の形名のJ-FETも使用可能です.

出力段がフルスイングするために必要なVSを,余裕を見て±30Vとすると,RSが2.2kΩではフルスイング時のISは±14mAとなります.

ごの時に,2SJl08/2SK370はゲート電流の流れるTr領域に触れますが,ゲート側が低インピーダンスであるため動作の支障にはなりません.ドライブ段TrのISに対する動作電流ISOはISの半分の7mAですが,ドライブ段はバイアス回路と局部帰還回路のJ-FETの動作に必要な電流の供給源であるため,ドライブ段Trのアイドリング電流IDOは,

IDO > IL + IDSS + ISO

= 2mA+5.5mA+7mA

=14.5mA

となります.

電圧増幅部の回路は'91年2月号発表のMOS-FETインバーテッド・ダーリントンアンプと同様の無帰還2段増幅です.

初段FETは出力段と同じ2SJ108/2SK370のゼロバイアス動作です.

図3の定数では,

IDO = ( RD ・ IDSS - VBE ) / RE

=(1kΩ×5.5mA-0.6V)/0.27kΩ

=18mA

となり,前記の条件を満足しています.IDSSが小さい場合はRSを増すなどの定数変更が必要となります.

なお,RSを増すのは構いませんが,逆に滅らした場合に,1.8kΩ以下で出力段が発振するようになります.

また電圧増幅部にNFBを掛けたり,出力段をダーリントン接続としても発振しやすくなります.

そのような回路は,発振を防止するために,MOS-FETのゲートと直列に抵抗を挿入する必要が出てきます.

本機の全回路を図6に示します.

[図6] 本機の回路

アンプ回路部分

電源回路部分

電圧増幅部の初段は,FETの耐圧をカバーするためカスコード接続としました.

電圧増幅部の電源には,電源ノイズとクロストークを減らすため,CRフィルターを入れました.

発振を防止するため,MOS-FETのドレインとアース間に接続するコンデンサーは,最短で配線します.

ここに使用するコンデンサーの種類は,安定性に大きく影響し,本機は1μFの積層セラミックコンデンサーを採用して,方形波出力波形でのリンギングを小さくすることができました.今回の製作では標準的な性能を保証するために,TrとFETは市販のコンプリメンタリーペアをそのまま使い,抵抗は5%級を無選別で用いました.

素子のペア選別を厳格に行い,精度の高い抵抗を使用し,プッシュプルのバランスを取れば,更に歪みを減らすことができます.本機で使用した素子の規格を表1に示します.

尚,本機は同程度の規格の素子で代用可能です.

[表1] FET,Trの規格 最大定格(Ta=25℃,*Tc=25℃)

電気的特性(Ta=25℃)

VGDS

IG

PD

Tj

IDSS

gm

Cis

電極接続 型名 (V)

(mA)

(mW)

℃

(mA)

(mS)

(pF)

2SJ108

25

-10

200

125

-2.6~ -20

22

105

2SK370

-40

10

200

125

2.6~20

2.2

30

D G S VDSS

ID

*PCH

TCH

VGS(t h)

gm

Cis

(V)

(A)

(W)

℃

(V)

(S)

(pF)

2SJ113

-100

-10

100

150

-2~ -5

2

1100

2SK399

100

10

100

150

2~5

2

800

G D S VCEO

IC

PC

Tj

fT

Cob

(V)

(mA)

(mW)

℃

hFE

(MHz)

(pF)

2SA1015

-50

-150

400

125

70~400

>80

4

2SC1815

50

150

400

125

70~700

>80

2

E C B VCEO

IC

PC

Tj

fT

Cob

(V)

(mA)

(W)

℃

hFE

(MHz)

(pF)

2SA1360

-150

‐50

5

150

150

200

2.5

2SC3423

150

50

5

150

150

200

1.8

E C B

シャシーはA4サイズのリードS4(300×200×60)です.

配線に無理をせず,部品の取り付けに離れ技を使わない限り,結果的に様式化した部品配置になっても仕方ありませんが,初めからそうした様式に従ったわけではなく,最大限部品や回路が望む配置を考えた結果です.

大電流回路の配線を短縮するために,22000μFのブロックコンデンサーはシャシーの内側に収納しました.

シャシーの加工は,放熱器の冷却を良くするため放熱器の取り付け部分をくり抜き,剛性を高めるため厚肉のアルミアングルで補強しました.

シャシーの熔接痕はヤスリで平らに削り取ってから塗装すると椅麗な仕上りにできます.

前面のデコレーションは,ワープロで黒いビニールシートに金色のインクリボンで印刷した自作のステッカーです.

基板については,プリント基板の銅箔は配線として使用する気になれません.

また蛇の目基板は,配線や部品を付け替える際に,穴づまりや,銅箔の剥がれ,半田ブリッジになりやすく,作業性がよくありません.

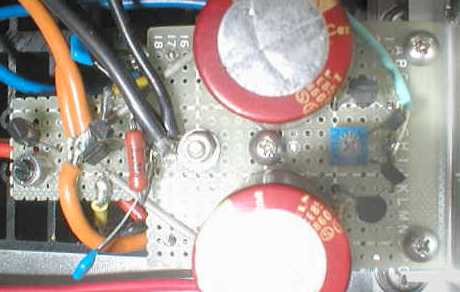

そのため本機の基板は,図7のように,蛇の目基板の銅箔をエッチング液で取り除き,リード線を通す穴を直径2mmに拡大し,配線を引き出す箇所には太さ0.8mmの単線を絡げてあります.

基板の上側の部品配置 |

|

|

|

基板の下側の部品配置 |

|

|

|

基板からMOS‐FETへの配線を短くするために,基板の取り付け位置と部品配置に,特に気を配りました.

2個のドライブ段Trの間に,アルミアングルの放熱板を抱き合わせて取り付けてありますが,この放熱板は基板のアースと接続して,シャシーには接触しないようにしてあります.

コンプリメンタリーFET同士では温度特性が不揃いなため,熱結合してもドリフトするので,本機では熱結合していません.

部品は基板の上下両面に取り付けてあり,配線は立体交差しているため,製作する時は間違いがないか良く回路図と照合して確かめるようにします.

電源回路は,ブロックコンデンサーの端子からLchとRchの2系統に分けて配線し,電圧増幅部電源の100Ωはラグ板に取り付けて,出力段のアイドリング電流をチェックするための抵抗0.47Ωは端子台に取り付けました.

出力信号はQ8,Q9のゲートと2.2kΩのアース側から取り出すのが理にかなってます.

従って,Q10,Q11のソースから Q8,Q9のゲートヘ配線して,そこから出力端子へ配線します.

一方のアース側は電源から2.2kΩヘ,そして出力端子へと配線します.整流ダイオードの配線からは強烈なリップルノイズを放出するため,他の配線と干渉しないように引き回します.

MOS-FETはゲートの配線をオープンで通電すると,入力容量にチャージしているゲート電圧のために,過大なドレイン電流が流れて破壊することがあるので要注意です.

調整前はVR1とVR2の抵抗値を最小にしておきます.

最初に電源を入れる時,もしもの場合に備えてMOS-FETのドレインと電源の間に10Ω10Wの抵抗を接続しておきます.

電源を入れて,出力DC電圧が±2V以内,10Ω両端の電圧が10V以下であるか確認します.

異常なければ10Ωを取り外し,正規の配線に戻します.

調整は始めに,アイドリング電流を1Aとするため,VR2を調整して0.47Ω両端の電圧を0.47Vにします.

もしVR2を最大にしても0.47Vに満たない場合はVR2と直列に1~2kΩの抵抗を入れ,逆にVR2を最小としても0.47Vを越える場合はツェナーダイオードHZ‐9LをHZ‐7Lに交換します.

アイドリング電流の設定後は0.47Ωを短絡しておきます.

次に出力DC電圧を0VとするためVR1を調整しますが,電源投入時の冷えている状態から暖まって熱的な安定状態に達するまで出力DC電圧が変動するため,どの状態で0Vとするか決め兼ねます.

本機は変動幅のおよその中心を0Vとしています.VR1を回して出力DC電圧が増加する場合は,Q1のソースの390Ω

をQ2のソースヘつなぎ換えます.配線の引き回しとアースポイントは,出力にヘッドフォンをつなぎ耳で聞いて,ノイズとクロストークが最小となるようにしました.

以上の調整をした後の測定で,後述の特性を得ることができました.

ソースフォ・ロワーに変更した場合を比較の対象にしてボルテージ・ミラーの優秀性を示すつもりでしたが,基本の回路が優秀であるため,ソース・フォロワの方も資質の素晴らしさを発揮してくれました.

ボルテージ・ミラーからソース・フォロワヘの変更は,図6,図7に示すように局部帰還のFETを取り外して抵抗を交換するだけで簡単にできるので,1台のアンプで2倍楽しめます.

変更後アイドリング電流が少し増加するので,再調整を要します.

なお,この回路変更をスイッチ等で行わない方が無難です.

配線が長くなれば発振しやすくなり,スイッチの接触不良や動作中の切り換えはスピーカーの損傷を招くからです.また,既にあるソース・フォロワのアンプをボルテージ・ミラーに変更

する場合は,前述したボルテージ・ミラーとしての制約を満たしていなければなりません.

図8の周波数特性と,図9のクロストーク特性については,ソース・フォロワとボルテージ・ミラーに差が無く,可声帯域内での特性は良好です.

高域のレスボンスが伸びない原因は,高い周波数の信号電流がMOS-FETの入力容量を通過してしまうことで,ゲート-ソース間にかかる信号電圧が減少するからです.

図10の歪み率特性は,各周波数ごとを平行移動したようにボルテージ・ミラーの方が低く,低い周波数では局部帰還の効果が高いために歪み率が低くなっています.

図11のダンピング・ファクター特性は,ボルテー・ジミラーの場合低域で1000以上もありますが600Hzから100kHzくらいの間は一直線に下降しています.

この原因も,MOS-FETの入力容量のため周波数が高くなると局部帰還量が減少するからです.

一方,ソース・フォロワの場合,可聴帯域内は20くらいにほぼ一定しています.このように互いの特性はまるで性格が違い,これが音質を分ける要因となっています.

次に10kHz方形波による抵抗負荷と容量負荷の出力波形の写真を示します.

立上がりを部分拡大した波形を重ねて表示し,リンギングを見やすくしてあります.

| ソース・フォロワ | ボルテージ・ミラー |

8Ω負荷 4Vp-p |

8Ω負荷 4Vp-p |

|

|

0.1μF負荷 |

0.1μF負荷 |

|

|

0.47μF負荷 |

0.47μF負荷 |

|

|

8Ω+0.1μF負荷 4Vp-p |

8Ω負荷 55Vp-p |

|

|

ソース・フォロワとボルテージ・ミラーの両方とも安定性が高く,容量負荷に対しても発振することはありません.

この安定性と高域特性の向上とは相反する関係にあり,両立が難しいところです.本機は必要以上に高域まで特性を伸ばすことをしなかったため,高い安走性が得られました.

電源ON-OFF時のショックノイズは0.5Vp-p以下と少なく,残留ノイズはRchが140μV,Lchが130μVとこれも少なく,静けさの中で電源トランスの鳴きが余計気になります.

放熱器の温度は,設置場所の風通しが良ければ,手で触れていられないほどの熱さとはなりません.

音質はボルテージ・ミラーがナチュラルなしっとり派,ソース・フォロワは低減の太い華やか派と,それぞれに個性を主張し,どちらも捨て難い存在で,その選択に悩みますが,それも製作者ならばこそ味わえる贅沢です.

Copyright © 1997

Shinichi Kamijo. All rights reserved.

最終更新日: 2007/01/02 09:36:51 +0900